Pinout และบล็อกไดอะแกรมของสายเคเบิล PL-USB2-Blaster

PL-USB2-Blaster เป็นส่วนประกอบสำคัญของซีรี่ส์สายเคเบิลดาวน์โหลด FPGA ของ Intel ทำให้สามารถกำหนดค่าIntel® FPGAs ผ่านการเชื่อมต่อ USBบทความนี้ให้รายละเอียดเกี่ยวกับการออกแบบและฟังก์ชั่นรวมถึง pinout, คุณสมบัติ, บล็อกไดอะแกรม, การเชื่อมต่อและข้อมูลเฉพาะเรามุ่งมั่นที่จะสำรวจรายละเอียดทางเทคนิคของอุปกรณ์ แต่ยังรวมถึงความสะดวกและประสิทธิผลที่นำไปสู่การกำหนดค่า FPGAแคตตาล็อก

PL-USB2-Blaster คืออะไร?

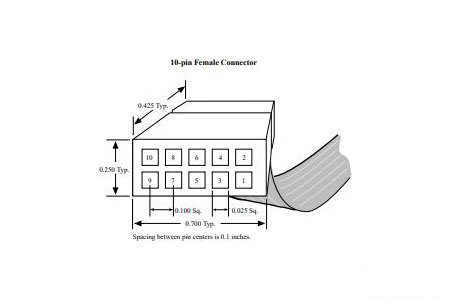

ที่ PL-USB2-Blaster เป็นส่วนประกอบที่ยอดเยี่ยมในซีรี่ส์สายเคเบิลดาวน์โหลดIntel® FPGA ซึ่งอำนวยความสะดวกในการถ่ายโอนข้อมูลที่มีประสิทธิภาพระหว่างคอมพิวเตอร์และ FPGA ผ่านการเชื่อมต่อ USBสายเคเบิลนี้ช่วยเพิ่มต้นแบบการทำซ้ำและการเขียนโปรแกรมการผลิตโดยการถ่ายทอดข้อมูลการกำหนดค่าผ่านส่วนหัว 10 พินมาตรฐานบนแผงวงจรการจับฟังก์ชั่นหลักของ PL-USB2-Blaster นั้นใช้สำหรับการปรับใช้ที่มีประสิทธิภาพในขั้นตอนต่าง ๆ ของการพัฒนา FPGAอุปกรณ์นี้ช่วยให้มั่นใจได้ว่าการบูรณาการอย่างราบรื่นในสภาพแวดล้อมการพัฒนาที่หลากหลายโดดเด่นด้วยความสามารถในการส่งข้อมูลที่รวดเร็วและสอดคล้องกัน

ในระหว่างขั้นตอนการทำต้นแบบซ้ำจำเป็นต้องมีความแม่นยำและความคล่องตัวPL-USB2-Blaster รองรับการอัปโหลดการกำหนดค่าที่อัปเดตอย่างรวดเร็วทำให้การทดสอบอย่างรวดเร็วและการปรับการตั้งค่า FPGAความคล่องตัวนี้เป็นประโยชน์ในสภาพแวดล้อมที่จำเป็นต้องทำซ้ำบ่อยครั้งในการออกแบบปรับแต่งและแก้ไขปัญหาทันทีความสอดคล้องในประสิทธิภาพเป็นสิ่งจำเป็นในการเขียนโปรแกรมการผลิตPL-USB2-Blaster รับประกันการเขียนโปรแกรมที่แม่นยำของการกำหนดค่าขั้นสุดท้ายใน FPGA เพื่อให้มั่นใจถึงความน่าเชื่อถือในแอปพลิเคชันการใช้งานปลายทางความสอดคล้องนี้ช่วยลดความคลาดเคลื่อนและเพิ่มประสิทธิภาพโดยเฉพาะอย่างยิ่งเมื่อการเขียนโปรแกรมจำนวนมากของหน่วย

Pinout of Pl-USB2-blaster

|

หมายเลขพิน |

ชื่อพิน |

คำอธิบายฟังก์ชั่น |

|

1 |

DCL |

พิน DCL นั้นดีสำหรับการแพร่กระจายสัญญาณนาฬิกา

สำหรับการดำเนินการแบบซิงโครนัสเป็นสิ่งสำคัญที่จะลดเสียงรบกวนและรักษา

การเชื่อมต่อที่มั่นคงคล้ายกับแนวทางการออกแบบวงจรความถี่สูง |

|

2 |

gnd |

กราวด์ (GND) ทำหน้าที่เป็นแรงดันอ้างอิง

การต่อสายดินที่สอดคล้องและเชื่อถือได้เพื่อป้องกันความแตกต่างในระดับสัญญาณ

และลดปัญหาเช่นลูปภาคพื้นดิน |

|

3 |

conf_done |

พิน conf_done บ่งบอกถึงความสมบูรณ์ของอุปกรณ์

การกำหนดค่าการตรวจสอบพินนี้ใช้สำหรับการตรวจสอบความสำเร็จ

การเริ่มต้นของอุปกรณ์ต่อพ่วง |

|

4 |

VOCC (TRGT) |

พิน VOCC จ่ายพลังงานให้กับระบบเป้าหมายด้วยก

มุ่งเน้นไปที่การส่งแรงดันไฟฟ้าที่ถูกต้องเพื่อหลีกเลี่ยงภายใต้หรือแรงดันไฟฟ้ามากเกินไป

เงื่อนไขการใช้วิธีการควบคุมพลังงาน |

|

5 |

nconfig |

PIN NCONFIG อำนวยความสะดวกในการกำหนดค่าอุปกรณ์ใหม่

การเปิดใช้งานการสร้างความมั่นใจในการรีเซ็ตหรือ reprogramming จะทำได้โดยไม่ต้อง

การขัดจังหวะ |

|

6 |

NCE |

PIN NCE (Chip Onable) ควบคุมสถานะการเปิดใช้งานของ

อุปกรณ์ที่ต้องการการยืนยันที่เหมาะสมในการเปิดใช้งานอุปกรณ์เมื่อจำเป็น

คล้ายกับการควบคุมเปิดใช้งานสัญญาณในวงจรรวม |

|

7 |

ข้อมูล |

DataOut รับผิดชอบการส่งออกข้อมูลโดยมุ่งเน้น

ในการส่งสัญญาณที่สะอาดเพื่อปกป้องความสมบูรณ์ของข้อมูลและรวม

โปรโตคอลการตรวจสอบข้อผิดพลาดต่อการทุจริตข้อมูล |

|

8 |

NCS |

PIN NCS (Chip Select) เปิดใช้งานอุปกรณ์เฉพาะ

ส่วนประกอบที่มีการควบคุมการเปิดใช้งานและการปิดการใช้งานเพื่อให้แน่ใจว่าถูกต้อง

ชิ้นส่วนของอุปกรณ์มีส่วนร่วมในเวลาที่เหมาะสม |

|

9 |

แอสดี้ |

ASDI ใช้สำหรับข้อมูลอินพุตโดยเน้นความต้องการ

อินพุตข้อมูลที่แม่นยำและทันเวลาการซิงโครไนซ์อินพุตคล้ายกับลำดับ

วงจรลอจิกเพื่อป้องกันการสื่อสารผิดพลาด |

|

10 |

gnd |

เช่นเดียวกับพิน 2 พิน 10 ให้สายดินอื่น

ชี้เน้นไปที่การใช้จุดกราวด์หลายจุดเป็นกลยุทธ์

พบได้ทั่วไปในระบบที่มีความแม่นยำสูงเพื่อเพิ่มความมั่นคงและประสิทธิภาพ |

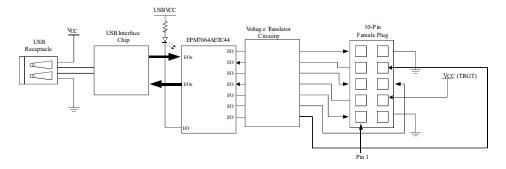

ไดอะแกรมฟังก์ชัน PL-USB2-Blaster

การกำหนดเส้นทางข้อมูลและเส้นทางการสื่อสาร

อินเทอร์เฟซโฮสต์คอมพิวเตอร์ทำหน้าที่เป็นจุดเริ่มต้นของการติดต่อสำหรับข้อมูลการกำหนดค่าทำหน้าที่เป็นสื่อกลางระหว่างซอฟต์แวร์ของคอมพิวเตอร์และฮาร์ดแวร์ PL-USB2-Blaster อินเทอร์เฟซนี้จะควบคุมโปรโตคอล USB 2.0 ความเร็วสูงเพื่ออำนวยความสะดวกในการส่งข้อมูลอย่างรวดเร็วและเชื่อถือได้หลังจากการรับข้อมูลหน่วยประมวลผลภายใน PL-USB2-Blaster ถือว่าการควบคุมหน่วยนี้ประกอบด้วยไมโครคอนโทรลเลอร์หรือ FPGA การแยกวิเคราะห์อย่างขยันขันแข็งตรวจสอบข้อผิดพลาดและรูปแบบข้อมูลที่เข้ามาเพื่อให้แน่ใจว่าเข้ากันได้กับส่วนประกอบที่ตามมา

หลังการประมวลผลข้อมูลจะอยู่ในหน่วยบัฟเฟอร์ชั่วคราวบัฟเฟอร์เหล่านี้จัดการกับความแตกต่างของเวลาระหว่างการไหลเข้าของข้อมูลความเร็วสูงและความเร็วในการประมวลผลแบบปลายน้ำที่แตกต่างกันจำเป็นต้องใช้วิธีการจัดการบัฟเฟอร์ที่มีประสิทธิภาพเนื่องจากลดการหยุดชะงักและการสูญเสียข้อมูลขั้นตอนต่อไปเกี่ยวข้องกับการส่งข้อมูลบัฟเฟอร์ไปยัง FPGA ผ่านเครือข่ายการกำหนดเส้นทางที่กำหนดไว้อย่างชัดเจนเครือข่ายนี้ที่เกี่ยวข้องกับมัลติเพล็กเซอร์, demultiplexers และเส้นทางเฉพาะได้ถูกสร้างขึ้นเพื่อรักษาความสมบูรณ์ของข้อมูลและการซิงโครไนซ์เครือข่ายการกำหนดเส้นทางที่ได้รับการปรับปรุงเป็นสิ่งสำคัญการกำหนดเส้นทางที่ไม่ดีสามารถนำไปสู่ข้อผิดพลาดการกำหนดค่าและปัญหาด้านประสิทธิภาพดังที่ระบุไว้ในแอปพลิเคชันที่ใช้งานได้จริง

การซิงโครไนซ์และการควบคุมเวลา

รากฐานที่สำคัญของสถาปัตยกรรมคือการสร้างนาฬิกาและระบบการกระจายซึ่งปรับเวลาการถ่ายโอนข้อมูลเพื่อให้แน่ใจว่าการทำงานที่ราบรื่นความแม่นยำในการกระจายนาฬิกามักจะถูกเน้นโดยผู้อื่นเพื่อใช้ในการรักษาการซิงโครไนซ์และประสิทธิภาพที่ดีที่สุดการรักษาความสมบูรณ์ของสัญญาณยังเป็นองค์ประกอบสำคัญของสถาปัตยกรรมของ PL-USB2-Blasterเทคนิคต่าง ๆ เช่นการส่งสัญญาณที่แตกต่างการจับคู่ความต้านทานและเส้นทางป้องกันถูกนำมาใช้เพื่อลดการย่อยสลายของสัญญาณและสัญญาณรบกวนแม่เหล็กไฟฟ้า (EMI)

กลไกการกำหนดค่าขั้นสูง

แผนภาพสถาปัตยกรรมยังแสดงกลไกสำหรับการตรวจจับข้อผิดพลาดและการแก้ไขเทคนิคต่าง ๆ เช่นการตรวจสอบความซ้ำซ้อนของวงจร (CRC) และอัลกอริทึมการตรวจจับข้อผิดพลาดอื่น ๆ จะระบุและแก้ไขความคลาดเคลื่อนของสตรีมข้อมูลโดยอัตโนมัติเพื่อให้มั่นใจถึงความน่าเชื่อถือของกระบวนการกำหนดค่าวิธีการเหล่านี้มีมูลค่าสูงในแอพพลิเคชั่นจำนวนมากสำหรับบทบาทของพวกเขาในการสร้างระบบที่แข็งแกร่งความสามารถในการกำหนดค่าใหม่แบบไดนามิกแสดงถึงคุณสมบัติที่ซับซ้อนอื่นของ PL-USB2-Blasterฟังก์ชั่นนี้ช่วยให้สามารถปรับเปลี่ยนการกำหนดค่า FPGA ได้โดยไม่หยุดการดำเนินการซึ่งเป็นลักษณะที่มีมูลค่าอย่างมากในสถานการณ์ที่ต้องปรับตัวและการหยุดทำงานน้อยที่สุด

ใช้ PL-USB2-Blaster

การติดตั้งไดรเวอร์

เริ่มต้นกระบวนการโดยการดาวน์โหลดและติดตั้งไดรเวอร์ที่ให้ไว้ของ Intelไดรเวอร์เหล่านี้ทำหน้าที่เป็นสะพานเชื่อมสำหรับการสื่อสารระหว่างสายเคเบิลและอุปกรณ์คอมพิวเตอร์ของคุณคุณจะพบคำแนะนำที่ครอบคลุมในแพ็คเกจไดรเวอร์โดยเสนอคำแนะนำทีละขั้นตอนผ่านการติดตั้ง

การเชื่อมต่อฮาร์ดแวร์

หลังจากติดตั้งไดรเวอร์ให้เชื่อมโยงสายเคเบิล PL-USB2-Blaster จากพอร์ต USB ของคอมพิวเตอร์ไปยังพอร์ตการเขียนโปรแกรมของอุปกรณ์เป้าหมายการเชื่อมต่อนี้ดีสำหรับการเตรียมส่วนประกอบฮาร์ดแวร์สำหรับการกำหนดค่าที่กำลังจะมาถึง

เปิดตัวโปรแกรมโปรแกรมเมอร์ Quartus Prime

ยิงซอฟต์แวร์ Intel Quartus Prime ตรงไปที่เครื่องมือ 'โปรแกรมเมอร์' และเลือกไฟล์การกำหนดค่าฮาร์ดแวร์ที่เหมาะสมอินเทอร์เฟซที่เป็นมิตรของซอฟต์แวร์ช่วยให้มั่นใจได้ว่ากระบวนการตั้งค่าอย่างง่ายทำให้สามารถปรับและกำหนดค่าได้อย่างรวดเร็ว

ดำเนินการกำหนดค่าอุปกรณ์

ปรับใช้โปรแกรมเมอร์ Quartus Prime เพื่อดำเนินการกำหนดค่าอุปกรณ์เลือกอุปกรณ์เป้าหมายจากรายการและอัปโหลดไฟล์โครงการที่เกี่ยวข้องเริ่มต้นลำดับการเขียนโปรแกรมและซอฟต์แวร์จะจัดการการถ่ายโอนข้อมูลโดยกำหนดค่าอุปกรณ์ FPGA ของคุณได้อย่างมีประสิทธิภาพ

บทบาทของ Signal Tap

สายเคเบิล PL-USB2-Blaster ขยายการรองรับการวิเคราะห์สัญญาณ Tap Logic ซึ่งเป็นเครื่องมือสำหรับการวิเคราะห์เชิงตรรกะที่เข้มงวดSignal Tap เสนอการวิเคราะห์ตรรกะแบบฝังตัวคุณลักษณะสำหรับการดีบักและตรวจสอบการออกแบบ FPGA

การตั้งค่าการแตะสัญญาณ

ภายในซอฟต์แวร์ Quartus Prime กำหนดค่าตัววิเคราะห์ Tap Tap Logic เพื่อจับภาพและตรวจสอบสัญญาณด้วยการกำหนดเงื่อนไขทริกเกอร์เฉพาะคุณสามารถควบคุมการรวบรวมข้อมูลอย่างพิถีพิถันช่วยในการระบุปัญหาภายในการออกแบบ FPGA

การใช้สายเคเบิล PL-USB2-Blaster ต้องการความเข้าใจอย่างลึกซึ้งของทั้งฮาร์ดแวร์และอาณาจักรซอฟต์แวร์การรวมเครื่องมือเหล่านี้เข้ากับกระบวนการออกแบบสามารถปรับปรุงวงจรการพัฒนาอย่างโดดเด่นและเพิ่มความน่าเชื่อถือของผลิตภัณฑ์ขั้นสุดท้ายการรวมกันของการตั้งค่าอย่างละเอียดและความสามารถในการวิเคราะห์ช่วยเพิ่มประสิทธิภาพของการพัฒนา FPGA อย่างแท้จริงปฏิบัติตามแนวทางเหล่านี้และใช้ประโยชน์จากคุณสมบัติที่ครอบคลุมของสายเคเบิล PL-USB2-Blaster และซอฟต์แวร์ Quartus Prime ช่วยให้สามารถสร้างเวิร์กโฟลว์การพัฒนาที่มีประสิทธิภาพและมีประสิทธิภาพทำให้มั่นใจได้ว่าประสิทธิภาพที่เหนือกว่าและความน่าเชื่อถือของการออกแบบ FPGA ของพวกเขา

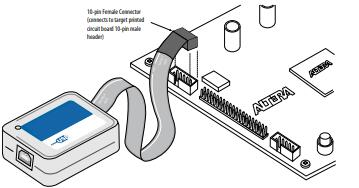

การเชื่อมต่อสายเคเบิลกับบอร์ด

มาตรการความปลอดภัยเพื่อการดำเนินงานที่ปลอดภัย

ก่อนอื่นให้แน่ใจว่าได้ตัดการเชื่อมต่อแหล่งพลังงานทั้งหมดก่อนที่จะเริ่มการเชื่อมต่อสายเคเบิลกับบอร์ดข้อควรระวังนี้ป้องกันอันตรายทางไฟฟ้าและป้องกันส่วนประกอบที่ละเอียดอ่อนบนบอร์ดอุปกรณ์

การสร้างการเชื่อมต่อ

เริ่มต้นด้วยการแนบสายดาวน์โหลด Intel FPGA เข้ากับพีซีดำเนินการเชื่อมต่อสายเคเบิลกับส่วนหัว 10 พินบนบอร์ดอุปกรณ์หลังจากตรวจสอบว่าการเชื่อมต่อทั้งหมดมีความปลอดภัยคืนแหล่งจ่ายไฟการเชื่อมต่อที่ปลอดภัยสามารถหลีกเลี่ยงข้อผิดพลาดข้อมูลและอำนวยความสะดวกในการสื่อสารที่แข็งแกร่งระหว่างอุปกรณ์

การติดตั้งไดรเวอร์

หากระบบส่งสัญญาณความจำเป็นในการติดตั้งไดรเวอร์ฮาร์ดแวร์ใหม่ให้ออกจากตัวช่วยสร้างเริ่มต้นยึดตามแนวทางการติดตั้งของผู้ผลิตทำให้มั่นใจได้ว่าไดรเวอร์ที่เหมาะสมจะได้รับการติดตั้งอย่างเหมาะสมวิธีการนี้ช่วยบำรุงความสามารถในการทำงานที่ดีที่สุดของอุปกรณ์การยึดมั่นอย่างระมัดระวังกับคำแนะนำในการติดตั้งแบบขั้นตอนของ Intel สามารถป้องกันการติดตั้งที่ไม่สมบูรณ์ซึ่งอาจส่งผลให้เกิดข้อบกพร่องของระบบ

การแยกสายเคเบิล

ถอดแหล่งจ่ายไฟออกก่อนที่จะถอดสายเคเบิลเพื่อป้องกันความเสียหายทางไฟฟ้าที่อาจเกิดขึ้นดำเนินการโดยถอดปลั๊กสายเคเบิลออกจากบอร์ดอุปกรณ์ตามด้วยการตัดการเชื่อมต่อจากพีซีลำดับการขาดการเชื่อมต่อที่เหมาะสมสามารถลดความเสี่ยงที่เชื่อมโยงกับไฟกระชากอย่างกะทันหันการติดตามกระบวนการขาดการเชื่อมต่ออย่างเป็นระบบรองรับการมีอายุยืนยาวของส่วนประกอบฮาร์ดแวร์และสามารถลดค่าใช้จ่ายในการซ่อมแซมได้

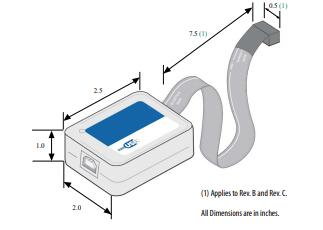

มิติ PL-USB2-Blaster

คำถามที่พบบ่อย [คำถามที่พบบ่อย]

1. จุดประสงค์ของ USB Blaster คืออะไร?

USB Blaster ช่วยให้ผู้ใช้พีซีสามารถโปรแกรมและกำหนดค่าอุปกรณ์ในระบบผ่านการเชื่อมต่อ USBเครื่องมือนี้ปรับปรุงกระบวนการพัฒนาให้คุณทำให้เป็นเพื่อนที่เชื่อถือได้ในการแสวงหาความคิดสร้างสรรค์และเทคนิคของพวกเขา

2. USB Blaster แตกต่างจาก USB Blaster II อย่างไร

USB Blaster ฉันรองรับวงจร JTAG ระหว่าง 2.5V และ 3.3Vในทางตรงกันข้าม USB Blaster II มีช่วงแรงดันไฟฟ้าที่กว้างขึ้นตั้งแต่ 1.5V ถึง 5V และมีคุณสมบัติขั้นสูงความสามารถรอบตัวของ USB Blaster II ช่วยให้เข้ากันได้กับระบบที่หลากหลายมากขึ้นซึ่งเป็นการขยายการใช้งานการปรับตัวนี้ช่วยเพิ่มฟังก์ชั่นการทำงานทำให้เป็นเครื่องมือที่เป็นที่ต้องการอย่างมากในสถานการณ์ที่ซับซ้อนมากขึ้น

3. ขั้นตอนในการติดตั้งไดรเวอร์ USB-blaster คืออะไร?

ประการแรกเชื่อมต่อ USB-blaster เข้ากับพีซีของคุณเมื่อเชื่อมต่อให้ทำตามพรอมต์บนหน้าจอเพื่อเลือกตัวเลือกการติดตั้งไดรเวอร์นำทางไปยังไดรเวอร์ที่อยู่ในไดเรกทอรีการติดตั้ง Quartus Prime และดำเนินการกับตัวช่วยสร้างการติดตั้งจนกว่ากระบวนการจะเสร็จสมบูรณ์อย่างสมบูรณ์วิธีการตรงไปตรงมานี้ช่วยให้มั่นใจได้ว่าการรวมเข้ากับสภาพแวดล้อมการพัฒนาของคุณอย่างราบรื่นความสะดวกในกระบวนการนี้ช่วยให้คุณสามารถมุ่งเน้นไปที่นวัตกรรมและความคิดสร้างสรรค์มากขึ้น

4. สิ่งที่จำเป็นต้องมีสำหรับการใช้สายดาวน์โหลด Intel FPGA

เริ่มต้นด้วยการติดตั้งไดรเวอร์ที่เหมาะสมในระบบของคุณขั้นตอนเริ่มต้นนี้มีความสำคัญต่อจากนั้นกำหนดค่าฮาร์ดแวร์ผ่านซอฟต์แวร์ Intel Quartus® Primeการเตรียมการนี้ปรับการตั้งค่าของคุณเพื่อประสิทธิภาพและประสิทธิภาพที่ดีที่สุด

5. Intel แนะนำอะไรสำหรับการใช้สายเคเบิลดาวน์โหลด Intel FPGA ที่ดีที่สุด?

Intel ให้คำแนะนำอย่างยิ่งกับการใช้ซอฟต์แวร์ Quartus Prime เวอร์ชันล่าสุดด้วยการอัปเดตด้วยการทำซ้ำล่าสุดทำให้ผู้อื่นสามารถเข้าถึงคุณสมบัติที่ได้รับการปรับปรุงและประสิทธิภาพที่ดีขึ้นการฝึกฝนนี้ช่วยให้มั่นใจได้ว่ามีความคล่องตัวมากขึ้นและทำให้การโต้ตอบแต่ละครั้งกับเครื่องมือมีประสิทธิผลมากขึ้น