# Single-Phase PWM Controller with Light-Load Efficiency Optimization

#### **FEATURES**

- 1.5-V to 19-V Conversion Voltage Range

- 4.5-V to 14-V Supply Voltage Range

- Voltage Mode Control

- Skip Mode at Light Load for Efficiency Optimization

- High Precision 0.5% Internal 0.8-V Reference

- Adjustable Output Voltage from 0.8 V to 0.7×V<sub>IN</sub>

- Internal Soft-Start

- Supports Pre-biased Startup

- Supports Soft-Stop

- Programmable Switching Frequency from 250 kHz to 1 MHz

- Overcurrent Protection

- Inductor DCR Sensing for Overcurrent

- R<sub>DS(on)</sub> Sensing for Zero Current Detection

- Overvoltage and Undervoltage Protection

- Open Drain Power Good Indication

- Internal Bootstrap Switch

- Integrated High-Current Drivers Powered by VCCDR

- Small 3 mm x 3 mm, 16-Pin QFN Package

## **APPLICATIONS**

- Server and Desktop Computer Subsystem Power Supplies

- DDR Memory and Termination Supply

- Distributed Power Supply

- General DC/DC Converter

## DESCRIPTION

TPS53211 is a single phase PWM controller with integrated high-current drivers. It is used for 1.5 V up to 19 V conversion voltage.

TPS53211 features a skip mode solution that optimizes the efficiency at light load condition without compromising the output voltage ripple. The device provides pre-biased startup, soft-stop, integrated bootstrap switch, power good function, EN/Input UVLO protection. It supports conversion voltages up to 19 V, and output voltages adjustable from 0.8 V to  $0.7 \times V_{IN}$ .

The TPS53211 is available in the 3 mm  $\times$  3 mm, 16-pin, QFN package (Green RoHs compliant and Pb free) and is specified from  $-40^{\circ}$ C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION

| TA            | PACKAGE     | ORDERABLE<br>DEVICE NUMBER | PINS | OUTPUT SUPPLY | MINIMUM<br>QUANTITY | ECO PLAN        |

|---------------|-------------|----------------------------|------|---------------|---------------------|-----------------|

| 40°C to 05°C  | Plastic QFN | TPS53211RGTR               | 16   | Tape and Reel | 3000                | Green (RoHS and |

| –40°C to 85°C | (RGT)       | TPS53211RGTT               | 16   | Mini Reel     | 250                 | no Pb/Br)       |

## **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                                                                |                     |                          | MIN                                                                                                           | MAX     | UNITS |  |

|----------------------------------------------------------------|---------------------|--------------------------|---------------------------------------------------------------------------------------------------------------|---------|-------|--|

| Input voltage range <sup>(2)</sup>                             | VCC, EN             |                          | -0.3                                                                                                          | 15      |       |  |

|                                                                | VCCDR               | -0.3                     | 7.7                                                                                                           |         |       |  |

|                                                                | BOOT                | dc                       | -0.3                                                                                                          | 36      |       |  |

|                                                                | BOOT to PHASE       | dc                       | -0.3                                                                                                          | 7.7     |       |  |

|                                                                | BOOT TO PHASE       | transient < 200 ns       | -5                                                                                                            | 7.7     | V     |  |

|                                                                | PHASE               | dc                       | -3                                                                                                            | 26      | V     |  |

|                                                                | PHASE               | transient < 200 ns       | -5                                                                                                            | 30      | -     |  |

|                                                                | FB, VSEN, OSC       | -0.3                     | 3.6                                                                                                           |         |       |  |

|                                                                | CCD CCN             | V <sub>VCC</sub> > 7.5 V | -0.7                                                                                                          | 6       |       |  |

|                                                                | CSP, CSN            | V <sub>VCC</sub> ≤ 7.5 V | -0.7                                                                                                          | VCC-1.5 |       |  |

|                                                                | UGATE               | -0.3                     | 36                                                                                                            |         |       |  |

| _                                                              | UGATE to PHASE,     | dc                       | -0.3                                                                                                          | 7.7     |       |  |

| Output voltage                                                 | LGATE               | transient < 200 ns       | -5                                                                                                            | 7.7     | V     |  |

| Output voltage range <sup>(3)</sup> Ground pins  Electrostatic | COMP                | -0.3                     | 3.6                                                                                                           |         |       |  |

|                                                                | PGOOD               |                          | -0.3                                                                                                          | 15      |       |  |

| Cround nine                                                    | GND                 |                          | -0.3                                                                                                          | 0.3     | V     |  |

| Ground pins                                                    | FBG                 | -0.3                     | 0.3                                                                                                           | V       |       |  |

| Electrostatic                                                  | Human Body Model (I |                          | 1500                                                                                                          | \/      |       |  |

| discharge                                                      | Charged Device Mode | el (CDM)                 | -0.3 -0.3 -0.3 -0.3 -0.3 ns -5 -3 ns -5 -0.3 -0.7 -0.7 -0.7 -0.7 -0.7 -0.3 -0.3 -0.3 -0.3 -0.3 -0.3 -0.3 -0.3 | 500     | V     |  |

| Storage junction temper                                        | erature             |                          | -55                                                                                                           | 150     | °C    |  |

| Operating junction tem                                         | perature            |                          | -40                                                                                                           | 150     | °C    |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## THERMAL INFORMATION

|                  |                                              | TPS53211 |       |  |

|------------------|----------------------------------------------|----------|-------|--|

|                  | THERMAL METRIC <sup>(1)</sup>                | QFN      | UNITS |  |

|                  |                                              | 16 PINS  |       |  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 51.3     |       |  |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 85.4     |       |  |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 20.1     | °C/W  |  |

| ΨЈТ              | Junction-to-top characterization parameter   | 1.3      | *C/VV |  |

| ΨЈВ              | Junction-to-board characterization parameter | 19.4     |       |  |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 6        |       |  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> All voltage values are with respect to the network ground terminal unless otherwise noted.

<sup>(3)</sup> Voltage values are with respect to the SW terminal.

## **RECOMMENDED OPERATING CONDITIONS**

|                            |                       |                          | MIN  | TYP MAX             | UNITS |  |  |

|----------------------------|-----------------------|--------------------------|------|---------------------|-------|--|--|

|                            | VCC                   |                          | 4.5  | 14                  |       |  |  |

|                            | EN                    | EN                       |      |                     |       |  |  |

|                            | VCCDR                 |                          | 4.5  | 7                   |       |  |  |

| Input voltage range        | BOOT                  | dc                       | -0.1 | 34                  |       |  |  |

|                            | BOOT to PHASE         | dc                       | -0.1 | 7                   |       |  |  |

|                            | BOOT to PHASE         | transient < 200ns        | -3   | 7                   | V     |  |  |

|                            | DUACE                 | dc                       | -1   | 24                  |       |  |  |

|                            | PHASE                 | transient < 200ns        |      |                     |       |  |  |

|                            | FB, VSEN, OSC         | FB, VSEN, OSC            |      |                     |       |  |  |

|                            | CCD CCN               | V <sub>VCC</sub> > 7.5 V | -0.1 | 5.5                 |       |  |  |

|                            | CSP, CSN              | V <sub>VCC</sub> ≤ 7.5 V | -0.1 | V <sub>VCC</sub> -2 |       |  |  |

|                            | UGATE                 | ·                        | -0.1 | 34                  |       |  |  |

|                            | LICATE to DUASE LOATE | dc                       | -0.1 | 7                   |       |  |  |

| Output voltage range       | UGATE to PHASE, LGATE | transient < 200 ns       | -3   | 7                   |       |  |  |

|                            | COMP                  |                          | -0.1 | 3.3                 | V     |  |  |

|                            | PGOOD                 |                          | -0.1 | 12                  |       |  |  |

| Craund nine                | GND                   | GND                      |      |                     |       |  |  |

| Ground pins                | FBG                   | FBG                      |      |                     |       |  |  |

| Junction temperature range | e, T <sub>J</sub>     |                          | -40  | 125                 | °C    |  |  |

| Operating free-air tempera | ture, T <sub>A</sub>  |                          | -40  | 85                  | °C    |  |  |

# **ELECTRICAL CHARACTERISTICS**(1)

over operating free-air temperature range, VCC = 12V, PGND = GND (unless otherwise noted)

|                                 | PARAMETER                           | TEST CONDITIONS                              | MIN   | TYP                  | MAX      | UNIT |

|---------------------------------|-------------------------------------|----------------------------------------------|-------|----------------------|----------|------|

| INPUT SUPP                      | LY                                  |                                              |       |                      |          |      |

| V <sub>VCC</sub>                | VCC supply voltage                  | Nominal input voltage range                  | 4.5   |                      | 12       | V    |

| V <sub>POR</sub>                | VCC POR threshold                   | Ramp up; EN ='HI'                            | 4.1   | 4.25                 | 4.4      | V    |

| V <sub>PORHYS</sub>             | VCC POR hysteresis                  | VCCDR POR hysteresis                         |       | 200                  |          | mV   |

| I <sub>CC_STBY</sub>            | Standby current                     | EN pin is low. V <sub>VCC</sub> = 12 V       |       |                      | 60       | μΑ   |

| R <sub>Boot</sub>               | Rds(on) of the boot strap switch    |                                              |       | 10                   |          | Ω    |

| DRIVER SUP                      | PPLY                                |                                              | •     |                      |          |      |

| V <sub>CCDR</sub>               | VCCDR Supply voltage                | Nominal input voltage range                  | 4.5   |                      | 7.0      | V    |

| V <sub>PORDR</sub>              | VCCDR POR threshold                 | Ramp up; EN ='HI'                            | 3.15  | 3.32                 | 3.50     | V    |

| V <sub>PORHYSDR</sub>           | VCCDR POR hysteresis                | VCCDR POR hysteresis                         |       | 220                  |          | mV   |

| I <sub>CCDR_STBY</sub>          | Standby current                     | EN pin is low. V <sub>VCC</sub> = 12 V       |       |                      | 100      | μΑ   |

| REFERENCE                       | <u> </u>                            |                                              |       |                      |          |      |

| V <sub>VREF</sub>               | VREF                                | Internal precision reference voltage         |       | 0.8                  |          | V    |

| TOL <sub>VREF</sub>             | VREF tolerance                      | Close loop trim. 0°C ≤ T <sub>J</sub> ≤ 70°C | -0.5% |                      | 0.5%     |      |

| ERROR AMP                       | PLIFIER                             |                                              | 1     |                      |          |      |

| UGBW <sup>(2)</sup>             | Unity gain bandwidth                |                                              | 14    |                      |          | MHz  |

| AOL <sup>(2)</sup>              | Open loop gain                      |                                              | 80    |                      |          | dB   |

| I <sub>FB(int)</sub>            | FB Input leakage current            | Sourced from FB pin                          |       | 10                   |          | nA   |

| I <sub>EA(max)</sub>            | Output sinking and sourcing current |                                              |       | 2.5                  |          | mA   |

| SR <sup>(2)</sup>               | Slew rate                           |                                              |       | 5                    |          | V/µs |

| ENABLE                          |                                     |                                              | "     |                      | <u> </u> |      |

| V <sub>ENH</sub>                | EN logic high                       |                                              | 2.2   |                      |          | V    |

| V <sub>ENL</sub>                | EN logic low                        |                                              |       |                      | 600      | mV   |

| I <sub>EN</sub>                 | EN pin current                      |                                              |       |                      | 12       | μA   |

| SOFT STAR                       | Г                                   |                                              | "     |                      | <u> </u> |      |

| t <sub>SS_delay</sub>           | Delay after EN asserting            | EN = 'HI' to "switching enabled"             |       | 1024/f <sub>SW</sub> |          | ms   |

| t <sub>PGDELAY</sub>            | PGOOD startup delay time            | PG delay after soft-start begins             |       | 1560/f <sub>SW</sub> |          | ms   |

| RAMP                            |                                     |                                              | "     |                      | <u> </u> |      |

|                                 | Ramp amplitude                      | 4.5V < V <sub>VCC</sub> < 12 V               |       | 2                    |          | V    |

| PWM                             |                                     |                                              | "     |                      | <u> </u> |      |

| t <sub>MIN(on)</sub> (2)        | Minimum ON time                     |                                              | 40    |                      |          | ns   |

| D <sub>MAX</sub> <sup>(2)</sup> | Maximum duty cycle                  | f <sub>SW</sub> = 1 MHz                      | 70%   |                      |          |      |

|                                 | FREQUENCY                           | 1 -                                          |       |                      |          |      |

| f <sub>SW(typ)</sub>            | Typical switching frequency         | $R_{OSC} = 61.9 \text{ k}\Omega$             | 360   | 400                  | 440      | kHz  |

| f <sub>SW(min)</sub>            | Minumum switching frequency         | $R_{OSC} = 250 \text{ k}\Omega$              |       | 250                  |          | kHz  |

| f <sub>SW(max)</sub>            | Maximum switching frequency         | $R_{OSC} = 14 \text{ k}\Omega$               |       | 1                    |          | MHz  |

| f <sub>SW(tol)</sub>            | Switching frequency tolerance       | $R_{OSC} > 12.4 \text{ k}\Omega$             | -20%  |                      | 20%      |      |

| OVERCURRI                       |                                     | 1                                            | L.    |                      |          |      |

| V <sub>OC_TH</sub>              | CSP-CSN threshold for DCR sensing   | T <sub>A</sub> = 25°C                        | 17    | 20                   | 23       | mV   |

<sup>(1)</sup> See PS pin description for levels.(2) Ensured by design. Not production tested.

# **ELECTRICAL CHARACTERISTICS**(1) (continued)

over operating free-air temperature range, VCC = 12V, PGND = GND (unless otherwise noted)

|                                  | PARAMETER                                         | TEST CONDITIONS                                                                     | MIN  | TYP  | MAX  | UNIT |

|----------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|------|

| GATE DRIVE                       | RS                                                |                                                                                     |      |      |      |      |

| R <sub>HDHI</sub> <sup>(3)</sup> | High-side driver sourcing resistance              | (V <sub>BOOT</sub> – V <sub>PH</sub> ) forced to 5 V, high state                    |      | 1    |      | Ω    |

| R <sub>HDLO</sub>                | High-side driver sinking resistance               | (V <sub>BOOT</sub> – V <sub>PH</sub> ) forced to 5 V, low state                     |      | 0.5  |      | Ω    |

| R <sub>LDHI</sub>                | Low-side driver sourcing resistance               | (V <sub>CCDR</sub> - GND) = 5 V, high state                                         |      | 0.7  |      | Ω    |

| R <sub>LDLO</sub>                | Low-side driver sinking resistance                | V <sub>CCDR</sub> - GND = 5 V, low state                                            |      | 0.33 |      | Ω    |

| POWER GOO                        | OD .                                              |                                                                                     |      |      |      |      |

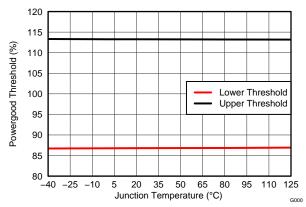

| $V_{PGDL}$                       | PG lower threshold                                | Measured at VSEN w/r/t VREF                                                         |      | 87%  | 89%  |      |

| V <sub>PGDU</sub>                | PG upper threshold                                | Measured at VSEN w//rt VREF                                                         | 110% | 113% | 116% |      |

| V <sub>PGHYS</sub>               | PG hysteresis                                     | Measured at VSEN w/r/t VREF                                                         |      | 3.5% |      |      |

| t <sub>OVPGDLY</sub>             | PG delay time at OVP                              | Time from VSEN out of +12.5% of VREF to PG low                                      |      | 2.3  |      | μs   |

| t <sub>UVPGDLY</sub>             | PG delay time at UVP                              | Time from VSEN out of –12.5% of VREF to PG low                                      |      | 2.3  |      | μs   |

| V <sub>INMINPG</sub>             | Minimum $V_{CC}$ voltage for valid PG at startup. | Measured at V <sub>VCC</sub> with 1 mA (or 2 mA) sink current on PG pin at startup. |      | 1    |      | V    |

| $V_{PGPD}$                       | PG pull-down voltage                              | Pull down voltage with 4 mA sink current                                            |      | 0.2  | 0.4  | V    |

| I <sub>PGLK</sub>                | PG leakage current                                | Hi-Z leakage current, apply 6.5 V in off state                                      | 7.8  | 12   | 16.2 | μA   |

| OUTPUT OV                        | ERVOLTAGE AND UNDERVOLTAGE                        | PROTECTION                                                                          |      |      |      |      |

| V <sub>OVth</sub>                | OVP threshold                                     | Measured at the VSEN wrt. VREF.                                                     | 110% | 113% | 116% |      |

| $V_{\text{UVth}}$                | UVP threshold                                     | Measured at the VSEN wrt. VREF.                                                     |      | 87%  | 89%  |      |

| t <sub>OVPDLY</sub>              | OVP delay time                                    | Time from VSEN out of +12.5% of VREF to OVP fault                                   |      | 2.3  |      | μs   |

| t <sub>UVPDLY</sub> (3)          | UVP delay time                                    | Time from VSEN out of –12.5% of VREF to UVP fault                                   |      | 80   |      | μs   |

| THERMAL SI                       | HUTDOWN                                           |                                                                                     |      |      |      |      |

| THSD <sup>(3)</sup>              | Thermal shutdown                                  | Latch off controller, attempt soft-stop                                             | 130  | 140  | 150  | °C   |

| THSD <sub>HYS</sub> (3)          | Thermal shutdown hysteresis                       | Controller starts again after temperature has dropped                               |      | 40   |      | °C   |

<sup>(3)</sup> Ensured by design. Not production tested.

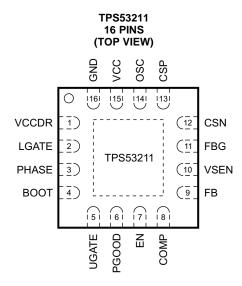

## **DEVICE INFORMATION**

## **PIN FUNCTIONS**

| PIN   | ]   |     | DESCRIPTION                                                                                                 |

|-------|-----|-----|-------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | I/O |                                                                                                             |

| BOOT  | 4   | I   | Supply input for high-side drive (boot strap pin). Connect capacitor from this pin to SW pin                |

| COMP  | 8   | 0   | Error amplifier compensation terminal. Type III compensation method is generally recommended for stability. |

| CSN   | 12  | Ι   | Current sense negative input.                                                                               |

| CSP   | 13  | I   | Current sense positive input                                                                                |

| EN    | 7   | I   | Enable.                                                                                                     |

| FB    | 9   | I   | Voltage feedback. Use for OVP, UVP and PGD determination.                                                   |

| FBG   | 11  | G   | Feedback ground for output voltage sense.                                                                   |

| GND   | 16  | G   | Logic ground and low-side gate drive return.                                                                |

| PHASE | 3   | 0   | Output inductor connection to integrated power devices.                                                     |

| LGATE | 2   | 0   | Low-side gate drive output.                                                                                 |

| OSC   | 14  | 0   | Frequency programming input.                                                                                |

| PGOOD | 6   | 0   | Power good output flag. Open drain output. Pull up to an external rail via a resistor.                      |

| UGATE | 5   | 0   | High-side gate drive output.                                                                                |

| VCC   | 15  | I   | Supply input for analog control circuitry.                                                                  |

| VCCDR | 1   | I/O | Bias voltage for integrated drivers.                                                                        |

| VSEN  | 10  | I   | Output voltage sense                                                                                        |

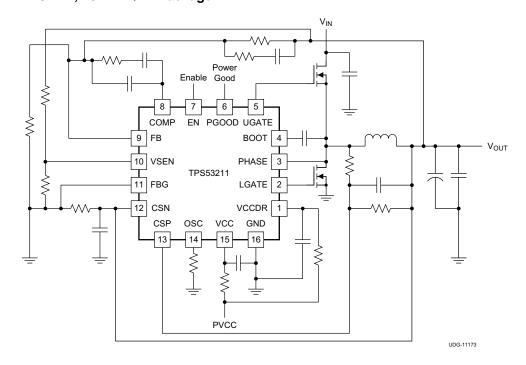

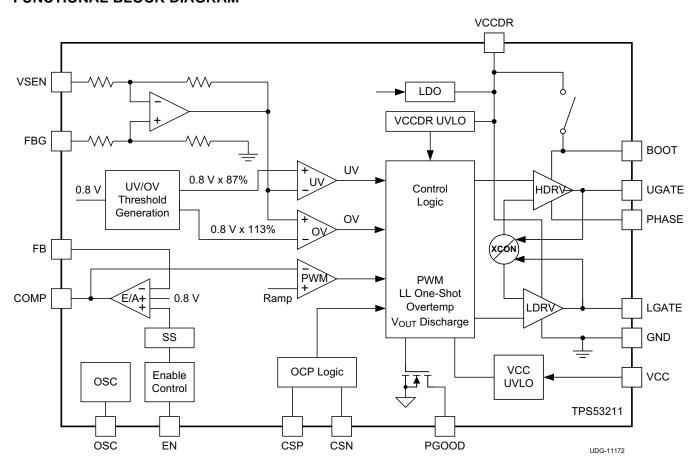

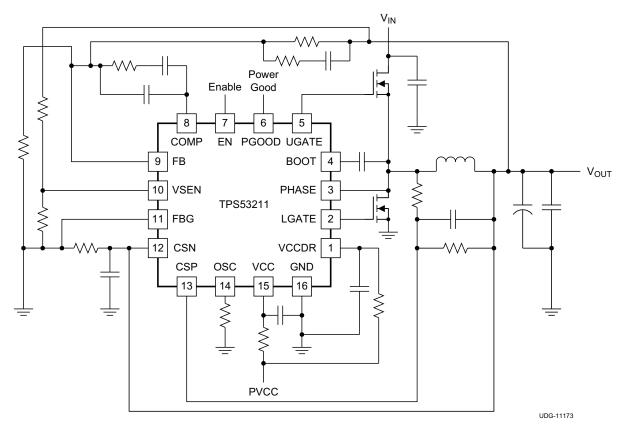

## **FUNCTIONAL BLOCK DIAGRAM**

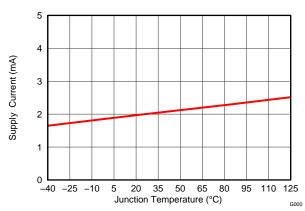

## **TYPICAL CHARACTERISTICS**

Figure 1. VCC Current vs. Junction Temperature

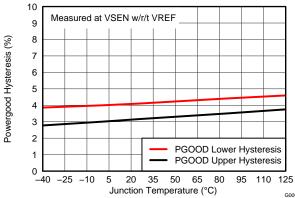

Figure 3. Power Good Hysteresis vs. Junction Temperature

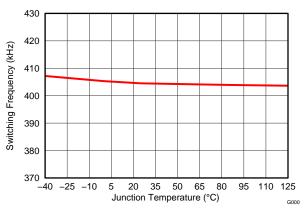

Figure 2. Switching Frequency vs. Junction Temperature

Figure 4. Power Good Threshold vs. Junction Temperature

#### DETAILED DESCRIPTION

#### Introduction

The TPS53211 is a single-channel synchronous buck controller with integrated high-current drivers. The TPS53211 is used for 1.5 V up to 19 V conversion voltage, and provides output voltage from 0.8 V to 0.7 V<sub>IN</sub>. It operates with programmable switching frequency ranging from 250 kHz to 1 MHz.

This device employs a skip mode solution that optimizes the efficiency at light-load condition without compromising the output voltage ripple. The device provides pre-bias startup, integrated bootstrap switch, power good function, EN/Input UVLO protection. The TPS53211 is available in the 3 mm by 3mm 16-pin QFN package and is specified from -40°C to 85°C.

## **Switching Frequency Setting**

The clock frequency is programmed by the value of the resistor connected from the OSC pin to ground. The switching frequency is programmable from 250 kHz to 1 MHz. The relation between the frequency and the OSC resistance is given by Equation 1.

$$f_{SW} = 200 + \frac{10^6}{(R_{OSC} \times 78.5) + 150}$$

where

- $R_{OSC}$  is the resistor connected from the OSC pin to ground in  $k\Omega$

- f<sub>SW</sub> is the desired switching frequency in kHz

# (1)

## **Soft-Start Function**

The soft-start function reduces the inrush current during the start-up. A slow rising reference voltage is generated by the soft-start circuitry and sent to the input of the error amplifier. When the soft-start ramp voltage is less than 800 mV, the error amplifier uses this ramp voltage as the reference. When the ramp voltage reaches 800 mV, a fixed 800 mV reference voltage is utilized for the error amplifier. The soft-start function is implemented only when VCC and VCCDR are above the respective UVLO thresholds and the EN pin is released.

When the soft-start begins, the device initially waits for 1024 clock cycles and then starts to ramp up the reference. After the reference voltage begins to rise, the PGOOD signal goes high after a 1560 clock-cycle delay.

## **UVLO Function**

The TPS53211 provides UVLO protection for the input supply (VCC) and driver supply (VCCDR). If the supply voltage is lower than UVLO threshold voltage minus the hysteresis, the device shuts off. When the voltage rises above the threshold voltage, the device restarts. The typical UVLO rising threshold is 4.25 V for VCC and 3.32 V for VCCDR. Hysteresis of 200 mV for VCC and 220 mV for VCCDR are also provided to prevent glitch.

#### **Overcurrent Protection**

The TPS53211 continuously monitors the current flowing through the inductor. The inductor DCR current sense is implemented by comparing and monitoring the difference between the CSP and CSN pins. DCR current sensing requires time constant matching between the inductor and the sensing network:

$$\frac{L}{DCR} = R \times C \tag{2}$$

TPS53211 has two level OC thresholds: 20 mV and 30 mV for the voltage between the CSP and CSN pins.

If the voltage between the CSP and CSN pins exceeds the 20 mV current limit threshold, an OC counter starts to increment to count the occurrence of the overcurrent events. The converter shuts down immediately when the OC counter reaches four (4). The OC counter resets if the detected current is lower than the OC threshold after an OC event. Normal operation can only be restored by cycling the VCC voltage.

If the voltage between the CSP and CSN pins is higher than 30 mV, the device latches off immediately. Normal operation can be restored only by cycling the VCC voltage.

The TPS53211 has thermal compensation to adjust the OCP threshold in order to reduce the influence of inductor DCR variation due to temperature change. The OCP level has a change rate of 0.35%/°C.

#### Overvoltage and Undervoltage Protection

The TPS53211 monitors the VSEN pin voltage to detect the overvoltage and undervoltage conditions. A resistor divider with the same ratio as on the FB input is recommended for the VSEN input. The overvoltage and undervoltage thresholds are set to  $\pm 13\%$  of  $V_{OLIT}$ .

When the VSEN voltage is greater than 113% of the reference, the overvoltage protection is activated. The high-side MOSFET turns off and the low-side MOSFET turns on. Normal operation can be restored only by cycling the VCC pin voltage.

When the VSEN voltage is lower than 87% of the reference voltage, the undervoltage protection is triggered and the PGOOD signal goes low. After 80  $\mu$ s, the controller is latched off with both the upper and lower MOSFETs turned off.

After both the undervoltage and overvoltage events, the device is latched off. Normal operation can be restored only by cycling the VCC pin voltage.

## **Power Good**

The TPS53211 monitors the output voltage through the VSEN. During start up, the power good signal delay after the reference begins to rise is 1560 clock cycles. After this delay, if the output voltage is within ±9.5% of the target value, PGOOD signal goes high.

At steady state, if the VSEN voltage is within 113% and 87% of the reference voltage, the power good signal remains high. If VSEN voltage is outside of this limit, PGOOD pin is pulled low by the internal open drain output. The PGOOD output is an open drain and requires an external pull-up resistor.

## **Over-Temperature Protection**

The TPS53211 continuously monitors the die temperature. If the die temperature exceeds the threshold value (140°C typical), the device shuts off. When the device temperature lowers to 40°C below the over-temperature threshold, it restarts and return to normal operation.

#### APPLICATION INFORMATION

The following example illustrates the design process and component selection for a single output synchronous buck converter using TPS53211. The schematic of a design example is shown in Figure 5. The specifications of the converter are listed in Table 1.

Table 1. Specification of the Single Output Synchronous Buck Converter

|                     | PARAMETER           | TEST CONDITION          | MIN  | TYP                    | MAX  | UNIT |

|---------------------|---------------------|-------------------------|------|------------------------|------|------|

| V <sub>IN</sub>     | Input voltage       |                         | 10.8 | 12                     | 13.2 | V    |

| V <sub>OUT</sub>    | Output voltage      |                         |      | 1.05                   |      | V    |

| V <sub>RIPPLE</sub> | Output ripple       | I <sub>OUT</sub> = 20 A |      | 1% of V <sub>OUT</sub> |      | V    |

| I <sub>OUT</sub>    | Output current      |                         |      | 20                     |      | Α    |

| f <sub>SW</sub>     | Switching frequency |                         |      | 400                    |      | kHz  |

Figure 5. Typical 12-V Input Application Circuit

## **Output Inductor Selection**

Determine an inductance value that yields a ripple current of approximately 20% to 40% of maximum output current. The inductor ripple current is determined by Equation 3:

$$I_{L(ripple)} = \frac{1}{L \times f_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$$

(3)

The inductor requires a low DCR to achieve good efficiency, as well as enough room above peak inductor current before saturation.

## **Output Capacitor Selection**

The output capacitor selection is determined by output ripple and transient requirement. When operating in CCM, the output ripple has three components:

$$V_{RIPPLE} = V_{RIPPLE(C)} + V_{RIPPLE(ESR)} + V_{RIPPLE(ESL)}$$

(4)

$$V_{RIPPLE(C)} = \frac{I_{L(ripple)}}{8 \times C_{OUT} \times f_{SW}}$$

(5)

$$V_{RIPPLE(ESR)} = I_{L(ripple)} \times ESR$$

(6)

$$V_{RIPPLE(ESL)} = \frac{V_{IN} \times ESL}{L}$$

(7)

When a ceramic output capacitor is chosen, the ESL component is usually negligible. In the case when multiple output capacitors are used, the total ESR and ESL should be the equivalent of the all output capacitors in parallel.

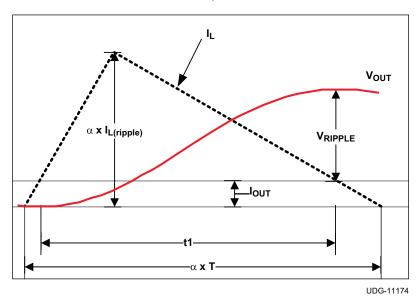

When operating in DCM, the output ripple is dominated by the component determined by capacitance. It also varies with load current and can be expressed as shown in Equation 8.

$$V_{RIPPLE(DCM)} = \frac{\left(\alpha \times I_{L(ripple)} - I_{OUT}\right)^{2}}{2 \times f_{SW} \times C_{OUT} \times I_{L(ripple)}}$$

where

$$\alpha = \frac{t_{ON(dcm)}}{t_{ON(ccm)}}$$

•  $\alpha$  is the DCM On-Time coefficient and can be expressed as

Figure 6. DCM V<sub>OUT</sub> Ripple Calculation

## **Input Capacitor Selection**

The selection of input capacitor should be determined by the ripple current requirement. The ripple current generated by the converter needs to be absorbed by the input capacitors as well as the input source. The RMS ripple current from the converter can be expressed as:

$$I_{IN(ripple)} = I_{OUT} \times \sqrt{D \times (1-D)}$$

where

$$D = \frac{V_{OUT}}{V_{IN}}$$

• D is the duty cycle and can be expressed as

To minimize the ripple current drawn from the input source, sufficient input decoupling capacitors should be placed close to the device. The ceramic capacitor is recommended due to the inherent low ESR and low ESL. The input voltage ripple can be calculated as below when the total input capacitance is determined:

$$V_{IN(ripple)} = \frac{I_{OUT} \times D}{f_{SW} \times C_{IN}}$$

(10)

## **Output Voltage Setting Resistors Selection**

The output voltage is programmed by the voltage-divider resistor, R1 and R2 shown in Figure 7. R1 is connected between FB pin and the output, and R2 is connected between the FB pin and FBG. The recommended value for R1 is between 1 k $\Omega$  and 5 k $\Omega$ . Determine R2 using Equation 11.

$$R1 = \left(\frac{0.8}{\left(V_{OUT} - 0.8\right)}\right) \times R1 \tag{11}$$

## **Compensation Design**

The TPS53211 employs voltage mode control. To effectively compensation the power stage and ensures fast transient response, Type III compensation is typically used.

The control to output transfer function can be described in Equation 12.

$$G_{CO} = 4 \times \frac{1 + s \times C_{OUT} \times ESR}{1 + s \times \left(\frac{L}{DCR + R_{LOAD}} + C_{OUT} \times (ESR + DCR)\right) + s^2 \times L \times C_{OUT}}$$

(12)

The output LC filter introduces a double pole, calculated in Equation 13.

$$f_{\rm DP} = \frac{1}{2 \times \pi \times \sqrt{L \times C_{\rm OUT}}} \tag{13}$$

The ESR zero of can be calculated calculated in Equation 14

$$f_{\mathsf{ESR}} = \frac{1}{2 \times \pi \times \mathsf{ESR} \times \mathsf{C}_{\mathsf{OUT}}} \tag{14}$$

Figure 7 shows the configuration of Type III compensation and typical pole and zero locations. Equation 15 through Equation 17 describe the compensator transfer function and poles and zeros of the Type III network.

$$G_{EA} = \frac{\left(1 + s \times C_{1} \times (R_{1} + R_{3})\right)\left(1 + s \times R_{4} \times C_{2}\right)}{\left(s \times R_{1} \times (C_{2} + C_{3})\right) \times \left(1 + s \times C_{1} \times R_{3}\right) \times \left(1 + s \times R_{4} \frac{C_{2} \times C_{3}}{C_{2} + C_{3}}\right)}$$

(15)

$$f_{Z1} = \frac{1}{2 \times \pi \times R_4 \times C_2} \tag{16}$$

$$f_{Z2} = \frac{1}{2 \times \pi \times (\mathsf{R}_1 + \mathsf{R}_3) \times \mathsf{C}_1} \cong \frac{1}{2 \times \pi \times \mathsf{R}_1 \times \mathsf{C}_1} \tag{17}$$

Figure 7. Type III Compensation Network Configuration

Figure 8. Type III Compensation Network Waveform

$$f_{P1} = 0$$

$$f_{P2} = \frac{1}{2 \times \pi \times R_3 \times C_1}$$

$$f_{P3} = \frac{1}{2 \times \pi \times R_4 \times \left(\frac{C_2 \times C_3}{C_2 + C_3}\right)} \cong \frac{1}{2 \times \pi \times R_4 \times C_3}$$

(18)

$$(19)$$

The two zeros can be placed near the double pole frequency to cancel the response from the double pole. One pole can be used to cancel ESR zero, and the other non-zero pole can be placed at half switching frequency to attenuate the high frequency noise and switching ripple. Suitable values can be selected to achieve a compromise between high phase margin and fast response. A phase margin higher than 45° is required for stable operation.

| CI | nanges from Original (September 2011) to Revision A                                                                                                  | Page |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed Input voltage range condition for CSP and CSN pins in ABSOLUTE MAXIMUM RATINGS table from " $V_{VCC} > 6.8$ " to " $V_{VCC} > 7.5$ "         | 2    |

| •  | Changed Input voltage range maximum specification for CSP and CSN pins in ABSOLUTE MAXIMUM RATINGS table from "5.3 V" to "6 V"                       | 2    |

| •  | Changed Input voltage range condition for CSP and CSN pins in ABSOLUTE MAXIMUM RATINGS table from " $V_{VCC} \le 6.8$ " to " $V_{VCC} \le 7.5$ "     | 2    |

| •  | Changed Input voltage range condition for CSP and CSN pins in RECOMMENDED OPERATING CONDITIONS table from " $V_{VCC} > 6.8$ " to " $V_{VCC} > 7.5$ " | 3    |

| •  | Changed Input voltage range maximum specification for CSP and CSN pins in RECOMMENDED OPERATING CONDITIONS table from "5 V" to "5.5 V"               | 3    |

| •  | Changed Input voltage range condition for CSP and CSN pins in RECOMMENDED OPERATING CONDITIONS table from " $V_{VCC} > 6.8$ " to " $V_{VCC} > 7.5$ " | 3    |

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TPS53211RGTR     | ACTIVE        | VQFN         | RGT                | 16   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 53211                   | Samples |

| TPS53211RGTT     | ACTIVE        | VQFN         | RGT                | 16   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 53211                   | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

**PACKAGE MATERIALS INFORMATION**

www.ti.com 11-Aug-2017

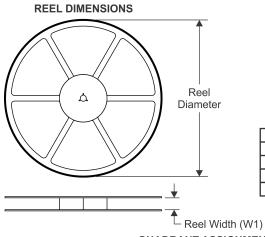

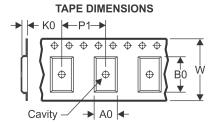

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

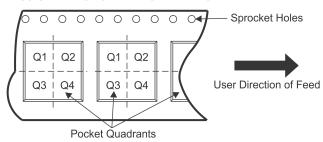

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS53211RGTR | VQFN            | RGT                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS53211RGTT | VQFN            | RGT                | 16 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 11-Aug-2017

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS53211RGTR | VQFN         | RGT             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS53211RGTT | VQFN         | RGT             | 16   | 250  | 210.0       | 185.0      | 35.0        |

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

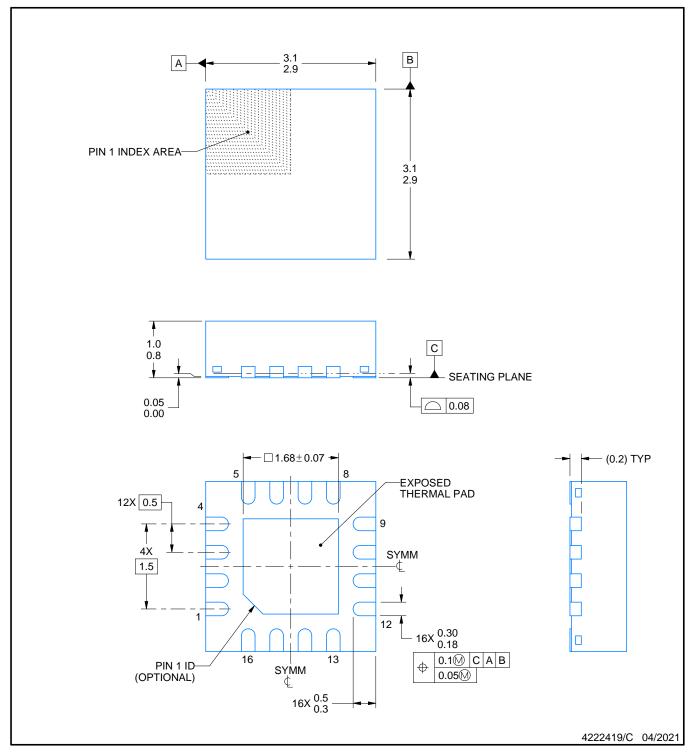

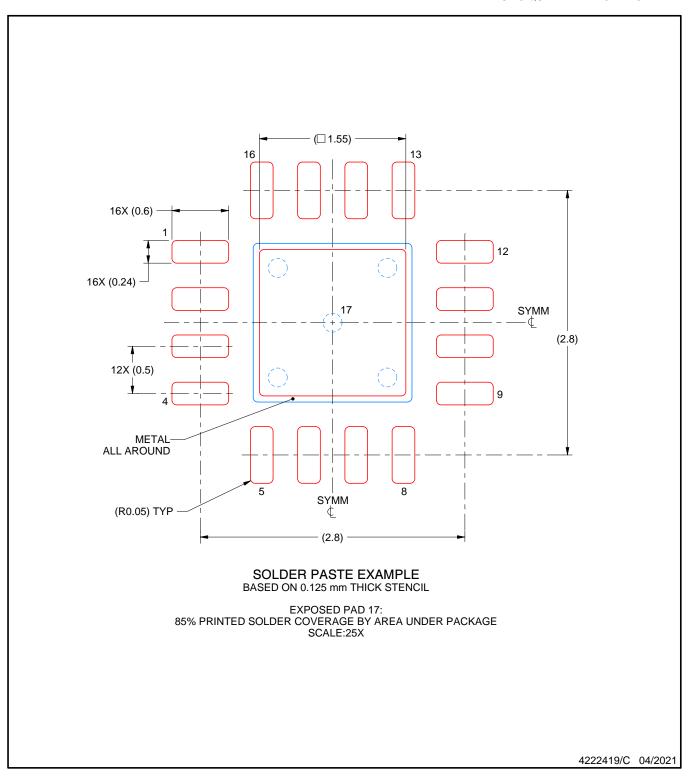

PLASTIC QUAD FLATPACK - NO LEAD

### NOTES:

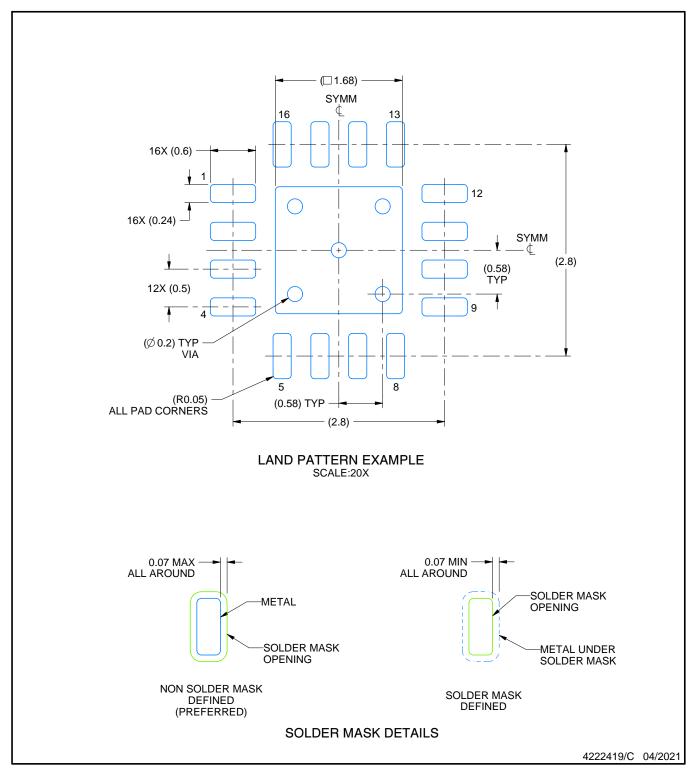

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated