# PRODUCT/PROCESS CHANGE NOTIFICATION

PCN MMS-MMY/13/8202 Dated 05 Nov 2013

M93C46, M93C56, M93C66, M93C76, M93C86 MICROWIRE serial access EEPROM / Industrial grade Redesign and upgrade to CMOSF8H

### **Table 1. Change Implementation Schedule**

| Forecasted implementation date for change                                                    | 29-Oct-2013 |

|----------------------------------------------------------------------------------------------|-------------|

| Forecasted availability date of samples for customer                                         | 29-Oct-2013 |

| Forecasted date for <b>STMicroelectronics</b> change Qualification Plan results availability | 25-Nov-2013 |

| Estimated date of changed product first shipment                                             | 04-Feb-2014 |

### **Table 2. Change Identification**

| Product Identification<br>(Product Family/Commercial Product) | M93C46, 56, 66, 76, 86 prod. families/Indus. grade          |  |  |  |  |

|---------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| Type of change                                                | Waferfab technology change                                  |  |  |  |  |

| Reason for change                                             | Line up to state-of-the-art of process                      |  |  |  |  |

| Description of the change                                     | Redesign and upgrade to the new CMOSF8H Process technology. |  |  |  |  |

| Change Product Identification                                 | Process Technology "K" for SO8N                             |  |  |  |  |

| Manufacturing Location(s)                                     |                                                             |  |  |  |  |

**A77.**

| Customer Part numbers list |  |

|----------------------------|--|

| Qualification Plan results |  |

| Customer Acknowledgement of Receipt                       | PCN MMS-MMY/13/8202 |

|-----------------------------------------------------------|---------------------|

| Please sign and return to STMicroelectronics Sales Office | Dated 05 Nov 2013   |

| □ Qualification Plan Denied                               | Name:               |

| □ Qualification Plan Approved                             | Title:              |

|                                                           | Company:            |

| □ Change Denied                                           | Date:               |

| □ Change Approved                                         | Signature:          |

| Remark                                                    |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

|                                                           |                     |

| 1                                                         |                     |

**47/**.

## **DOCUMENT APPROVAL**

| Name              | Function          |

|-------------------|-------------------|

| Leduc, Hubert     | Marketing Manager |

| Rodrigues, Benoit | Product Manager   |

| Pavano, Rita      | Q.A. Manager      |

**A7**/.

# PRODUCT / PROCESS CHANGE NOTIFICATION

# M93C46, M93C56, M93C66, M93C76, M93C86, 1-Kbit, 2-Kbit, 4-Kbit, 8-Kbit, 16-Kbit MICROWIRE serial access EEPROM / Industrial grade Redesign and upgrade to the CMOSF8H process technology

### What is the change?

The M93C46, M93C56, M93C66, M93C76 & M93C86, 1-Kbit, 2-Kbit, 4-Kbit, 8-Kbit and 16-Kbit MICROWIRE serial access EEPROM product families for industrial grade, currently produced using the CMOSF6SP 36% process technology at ST Ang Mo Kio (Singapore) 6" or at GLOBALFOUNDRIES (Singapore) 8" wafer diffusion plants, have been **redesigned** and will be **upgraded** to the **CMOSF8H** process technology at **ST Rousset** (France) 8" wafer diffusion plant.

This upgraded version in CMOSF8H allows offering:

- Write cycles up to 4 millions

- Data retention up to 200 years

The new M93C46, M93C56, M93C66, M93C76 and M93C86 in CMOSF8H version are functionally compatible with the current CMOSF6SP 36% version as per common datasheet rev. 13 – April 2013, attached.

These new M93C46, M93C56, M93C66, M93C76 and M93C86 are described in a common datasheet for M93**C**xx with following differences versus previous common datasheet:

- DC characteristic: I<sub>cc1</sub> standby supply current:

- Max 1  $\mu$ A at V<sub>CC</sub> = 1.8 V (was 2  $\mu$ A for previous version)

- Max 2  $\mu$ A at V<sub>CC</sub> = 2.5 V (was 5  $\mu$ A for previous version)

- <u>DC characteristic:</u> f<sub>c</sub> lock frequency:

- Max 2 MHz for V<sub>CC</sub> = 1.8 V (was 1 MHZ for previous version)

Concurrent to this change, the new M93C46, M93C56, M93C66, M93C76 and M93C86 in CMOSF8H will be assembled with 0.8 mil Copper wire when packaged in SO8N or in UFDFPN8 (MLP8).

### Why?

The strategy of STMicroelectronics Memory Division is to support our customers on a long-term basis. In line with this commitment, the qualification of the M93C46, M93C56, M93C66, M93C76 and M93C86 in the new CMOSF8H process technology will increase the production capacity throughput and consequently improve the service to our customers.

### When?

The production of the upgraded new M93C46, M93C56, M93C66, M93C76 and M93C86 with the new CMOSF8H will ramp up from November 2013 and shipments can start from end of January 2014 onward (or earlier upon customer approval).

### How will the change be qualified?

The new version of the new M93C46, M93C56, M93C66, M93C76 and M93C86 in CMOSF8H in CMOSF8H will be qualified using the standard ST Microelectronics Corporate Procedures for Quality & Reliability.

**Qualification Plan QPMMY1313** is included inside this document. Following **Qualification Reports** will be available Week 48 / 2013. :

- QRMMY1320 for M93C46

- QRMMY1319 for M93C56

- QRMMY1318 for M93C66

- QRMMY1317 for M93C76

- QRMMY1313 for M93C86

### What is the impact of the change?

- Form: Marking change (see **Device marking** paragraph)

- Fit: No change

- Function:

- Change on DC characteristic I<sub>CC1</sub> standby supply current

- Change on AC characteristic f<sub>c</sub> Clock frequency for 1.8 V

### How can the change be seen?

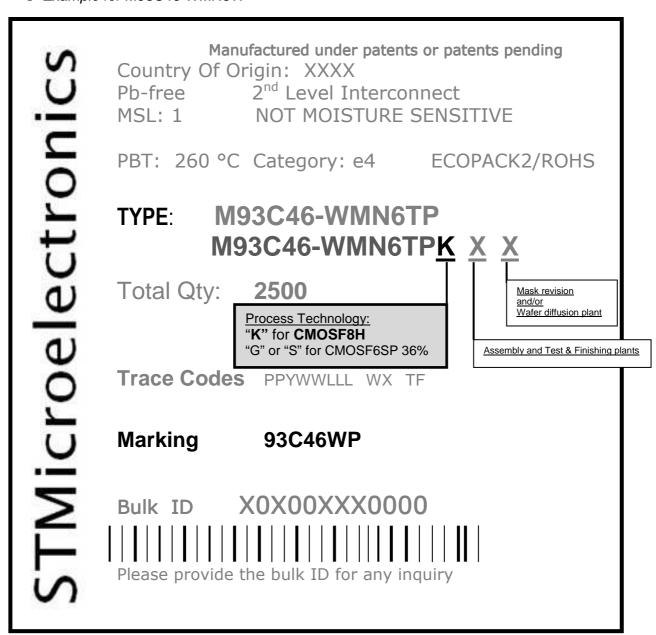

### - BOX LABEL MARKING

On the BOX LABEL MARKING, the difference is visible inside the **Finished Good Part Number**: the **process technology** identifier is "K" for the **upgraded version** in **CMOSF8H**, this identifier being "G" or "S" for the current version in CMOSF6SP 36%.

→ Example for M93C46-WMN6TP

### How can the change be seen?

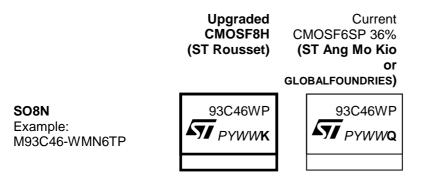

### - DEVICE MARKING

For the **SO8N** package, the difference is visible inside the trace code (*PYWWT*) where the last digit is "**K**" for the **upgraded version** in **CMOSF8H**, this digit being "G", "S" or "Q" for current versions.

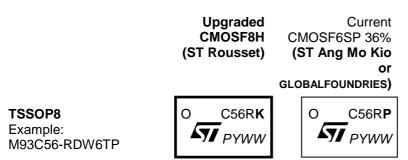

For the **TSSOP8** package, the difference is visible inside the product name where the last digit is "**K**" for the **upgraded version** in **CMOSF8H**, this digit being "P" for current version.

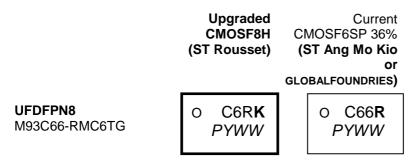

For the **UFDFPN8** package, the difference is visible inside the product name: **upgraded version** in **CMOSF8H** is **C6RK**, current version is C66R.

# **Appendix A- Product Change Information**

| Product family / Commercial products:                                                                    | M93C46, M93C56, M93C66, M93C76, M93C86                                                                                    |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                          | products families / Industrial grade                                                                                      |  |  |  |

| Customer(s):                                                                                             | All                                                                                                                       |  |  |  |

| Type of change:                                                                                          | Wafer fab process technology change                                                                                       |  |  |  |

| Reason for the change:                                                                                   | Line up to state-of-the-art of process                                                                                    |  |  |  |

| Description of the change:                                                                               | Redesign and upgrade to the new CMOSF8H Process technology.                                                               |  |  |  |

| Forecast date of the change: (Notification to customer)                                                  | Week 44 / 2013                                                                                                            |  |  |  |

| Forecast date of <a href="Qualification samples">Qualification samples</a> availability for customer(s): | See details in APPENDIX B                                                                                                 |  |  |  |

| Qualification Report availability:                                                                       | The Qualification Plan QPMMY1313 is included inside this document.  Qualification Reports will be available Wee 48 / 2013 |  |  |  |

| Marking to identify the changed product:                                                                 | Process Technology identifier "K" for CMOSF8H for SO8N.                                                                   |  |  |  |

| Description of the qualification program:                                                                | Standard ST Microelectronics Corporate Procedures for Quality and Reliability                                             |  |  |  |

| Product Line(s) and/or Part Number(s):                                                                   | See Appendix B                                                                                                            |  |  |  |

| Manufacturing location:                                                                                  | Rousset 8 inch wafer fab                                                                                                  |  |  |  |

| Estimated date of first shipment:                                                                        | Week 05 / 2014                                                                                                            |  |  |  |

# **Appendix B: Concerned Commercial Part Numbers:**

| Commercial<br>Part Numbers | Package | Samples availability        |

|----------------------------|---------|-----------------------------|

| M93C46-WDW6TP              | TSSOP8  | Available                   |

| M93C46-WMN6P               | SO8N    | No sample for tube delivery |

| M93C46-WMN6TP              | SO8N    | Available                   |

| M93C56-RDW6TP              | TSSOP8  | Week 50                     |

| M93C56-RMN6P               | SO8N    | No sample for tube delivery |

| M93C56-RMN6TP              | SO8N    | Week 50                     |

| M93C56-WDW6TP              | TSSOP8  | Week 47                     |

| M93C56-WMN6P               | SO8N    | No sample for tube delivery |

| M93C56-WMN6TP              | SO8N    | Week 47                     |

| M93C66-RMC6TG              | UFDFPN8 | Week 48                     |

| M93C66-WDW6TP              | TSSOP8  | Available                   |

| M93C66-WMN6P               | SO8N    | No sample for tube delivery |

| M93C66-WMN6TP              | SO8N    | Week 47                     |

| M93C76-WMN6TP              | SO8N    | Week 47                     |

| M93C86-WDW6TP              | TSSOP8  | Week 47                     |

| M93C86-WMN6P               | SO8N    | No sample for tube delivery |

| M93C86-WMN6TP              | SO8N    | Week 47                     |

### **Appendix C: Qualification Reports:**

See following pages

# M93Cxx Redesign and Upgrade to the CMOSF8H process technology Qualification Plan QPMMY1313 (2/4)

• The product vehicles used for the die qualification are presented in *Table 1*.

Table 1. Product vehicles used for die qualification

| Product | Silicon process technology | Wafer fabrication location | Package<br>description | Assembly plant location         |  |

|---------|----------------------------|----------------------------|------------------------|---------------------------------|--|

| М93Схх  | CMOSF8H                    | ST Rousset 8"              | CDIP8                  | Engineering assy <sup>(1)</sup> |  |

Note (1): CDIP8 is a engineering ceramic package used only for die-oriented reliability trials.

The package qualifications were mainly obtained by similarity. The product vehicle used for package qualification is presented in *Table 2*.

Table 2. Product vehicles used for package qualification

| Product    | Silicon process technology | Wafer fabrication location | Package description        | Assembly plant<br>location    |  |

|------------|----------------------------|----------------------------|----------------------------|-------------------------------|--|

|            |                            |                            | SO8N                       | ST Shenzhen /<br>Subcon Amkor |  |

| M95160 (1) | CMOSF8H                    | ST Rousset 8"              | TSSOP8                     | ST Shenzhen /<br>Subcon Amkor |  |

|            |                            |                            | UFDFPN8 (MLP8)<br>2 x 3 mm | ST Calamba /<br>Subcon Amkor  |  |

Note (1): Similar memory array using the same silicon process technology in the same diffusion fab. Package qualification results of M95160 are applicable to M93Cxx.

### 3

# M93Cxx Redesign and Upgrade to the CMOSF8H process technology Qualification Plan QPMMY1313 (3/4)

• The reliability test plan related to the new M93Cxx is presented as follows:

|      | Test short description                          |                                                                   |                      |                |                             |                        |

|------|-------------------------------------------------|-------------------------------------------------------------------|----------------------|----------------|-----------------------------|------------------------|

| Test | Method                                          | Conditions                                                        | Sample<br>size / lot | No. of<br>lots | Duration                    | Acceptance<br>Criteria |

|      | High temperature operating life after endurance |                                                                   |                      |                |                             |                        |

| EDD  | AEC-Q100-005                                    | 400 000 E/W cycles at 150 °C then:<br>HTOL 150 °C, 6v             | 80                   | 3              | 1008 hrs                    | 0/80                   |

| EDR  | Data retention after endurance                  |                                                                   |                      |                |                             |                        |

|      | AEC-Q100-005                                    | 400 000 E/W cycles at 150 °C then:<br>HTSL 150 °C                 | 80                   | 3              | 1008 hrs                    | 0/80                   |

| LTOL | Low temperature operating life                  |                                                                   |                      |                |                             |                        |

| LTOL | JESD22-A108                                     | -40 °C, 6v                                                        | 80                   | 3              | 1008 hrs                    | 0/80                   |

| HTSL | High temperature storage life                   |                                                                   |                      |                |                             |                        |

| ПІЗС | JESD22-A103                                     | Retention bake at 200 °C                                          | 80                   | 3              | 1008 hrs                    | 0/80                   |

|      | Program/erase e                                 | endurance cycling + bake                                          |                      |                |                             |                        |

| WEB  | Internal spec.                                  | 5 million cycles at 25 °C then: retention bake at 200 °C / 48 hrs | 80                   | 3              | 5 million cycles<br>/ 48hrs | 0/80                   |

# M93Cxx Redesign and Upgrade to the CMOSF8H process technology Qualification Plan QPMMY1313 (4/4)

|            | Test short description                        |                                                                          |    |          |                        |                       |

|------------|-----------------------------------------------|--------------------------------------------------------------------------|----|----------|------------------------|-----------------------|

| Test       | Method                                        | Method     Conditions     Sample size / lot     No. of lots     Duration |    | Duration | Acceptance<br>Criteria |                       |

| ESD        | Electrostatic dis                             | charge (human body model)                                                |    |          |                        |                       |

| HBM        | AEC-Q100-002<br>JESD22-A114                   | C = 100 pF, R = 1500 Ohms                                                | 27 | 3        | N/A                    | PASS<br>4000 V        |

| ESD        | Electrostatic discharge (machine model)       |                                                                          |    |          |                        |                       |

| MM         | AEC-Q100-003<br>JESD22-A115                   | C = 200 pF, R = 0 Ohms                                                   | 12 | 3        | N/A                    | PASS<br>400 V         |

| ECD        | Electrostatic discharge (charge device model) |                                                                          |    |          |                        |                       |

| ESD<br>CDM | AEC-Q100-011<br>JESD22-C101                   | Field induced charging method                                            | 18 | 3 (1)    | N/A                    | PASS<br>1500V         |

|            | Latch-up (currer                              | nt injection and over-voltage stress)                                    |    |          |                        |                       |

| LU         | AEC-Q100-004<br>JESD78B                       | At maximum operating temperature (150 °C)                                | 6  | 3        | N/A                    | Class II –<br>Level A |

Note (1): ESD CDM will be performed on 1 lot by package (SO8N, TSSOP8, UFDFPN8).

| Document Revision History |                                       |                      |  |  |  |  |  |

|---------------------------|---------------------------------------|----------------------|--|--|--|--|--|

| Date                      | Date Rev. Description of the Revision |                      |  |  |  |  |  |

| October 27, 2013          | 1.00                                  | First draft creation |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

|                           |                                       |                      |  |  |  |  |  |

| Source Documents & Reference Documen | ts |       |       |

|--------------------------------------|----|-------|-------|

| Source document Title                |    | Rev.: | Date: |

|                                      |    |       |       |

|                                      |    |       |       |

|                                      |    |       |       |

# M93C86xx M93C76xx M93C66xx M93C56xx M93C46xx

16-Kbit, 8-Kbit, 4-Kbit, 2-Kbit and 1-Kbit (8-bit or 16-bit wide) MICROWIRE serial access EEPROM

Datasheet - production data

### **Features**

- · Industry standard MICROWIRE bus

- Single supply voltage:

- 4.5 V to 5.5 V for M93Cx6

- 2.5 V to 5.5 V for M93Cx6-W

- 1.8 V to 5.5 V for M93Cx6-R

- Dual organization: by word (x16) or byte (x8)

- Programming instructions that work on: byte, word or entire memory

- Self-timed programming cycle with auto-erase:

5 ms

- READY/BUSY signal during programming

- 2 MHz clock rate

- · Sequential read operation

- Enhanced ESD/latch-up behavior

- More than 1 million write cycles

- More than 40 year data retention

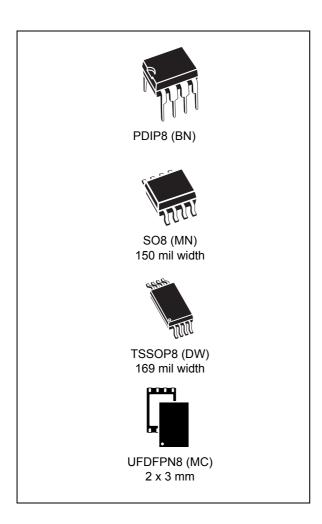

- Packages

- SO8, TSSOP8, UFDFPN8 packages: RoHS-compliant and Halogen-free (ECOPACK2®)

- PDIP8 package:

RoHS-compliant (ECOPACK1®)

Table 1. Device summary

| Reference  | Part<br>number | Memory<br>size | Supply<br>voltage |

|------------|----------------|----------------|-------------------|

| M93C46xx   | M93C46         | 1 Kbit         | 4.5 V to 5.5 V    |

| 10193040XX | M93C46-W       | 1 Kolt         | 2.5 V to 5.5 V    |

|            | M93C56         |                | 4.5 V to 5.5 V    |

| M93C56xx   | M93C56-W       | 2 Kbit         | 2.5 V to 5.5 V    |

|            | M93C56-R       |                | 1.8 V to 5.5 V    |

|            | M93C66         |                | 4.5 V to 5.5 V    |

| M93C66xx   | M93C66-W       | 4 Kbit         | 2.5 V to 5.5 V    |

|            | M93C66-R       |                | 1.8 V to 5.5 V    |

| M93C76xx   | M93C76-W       | 8 Kbit         | 2.5 V to 5.5 V    |

| INIBOUTURX | M93C76-R       | O KUIL         | 1.8 V to 5.5 V    |

| M93C86xx   | M93C86         | 16 Kbit        | 4.5 V to 5.5 V    |

| INIBOCOUXX | M93C86-W       | TO KUIL        | 2.5 V to 5.5 V    |

# **Contents**

| 1  | Des    | cription  |                                             | 6  |

|----|--------|-----------|---------------------------------------------|----|

| 2  | Con    | necting   | to the serial bus                           | 8  |

| 3  | Оре    | rating fe | eatures                                     | 9  |

|    | 3.1    | Supply    | y voltage (V <sub>CC</sub> )                | 9  |

|    |        | 3.1.1     | Operating supply voltage (V <sub>CC</sub> ) |    |

|    |        | 3.1.2     | Power-up conditions                         |    |

|    |        | 3.1.3     | Power-up and device reset                   | 9  |

|    |        | 3.1.4     | Power-down                                  | 9  |

| 4  | Mem    | nory org  | ganization                                  | 10 |

| 5  | Instr  | uctions   | S                                           | 11 |

|    | 5.1    | Read [    | Data from Memory                            | 13 |

|    | 5.2    | Erase     | and Write data                              | 13 |

|    |        | 5.2.1     | Write Enable and Write Disable              |    |

|    |        | 5.2.2     | Write                                       | 13 |

|    |        | 5.2.3     | Write All                                   | 15 |

|    |        | 5.2.4     | Erase Byte or Word                          | 16 |

|    |        | 5.2.5     | Erase All                                   | 16 |

| 6  | REA    | DY/BUS    | SY status                                   | 17 |

| 7  | Initia | al delive | ery state                                   | 17 |

| 8  | Cloc   | k pulse   | counter                                     | 18 |

| 9  | Max    | imum ra   | ating                                       | 19 |

| 10 | DC a   | and AC    | parameters                                  | 20 |

| 11 | Pacl   | kage me   | echanical data                              | 27 |

| 12 | Part   | numbe     | ring                                        | 31 |

| M93C86xx | M93C76xx | M93C66xx | M93C56xx | M93C46xx |

|----------|----------|----------|----------|----------|

|----------|----------|----------|----------|----------|

Contents

# List of tables

| Table 1.  | Device summary                                                               | 1   |

|-----------|------------------------------------------------------------------------------|-----|

| Table 2.  | Memory size versus organization                                              | 6   |

| Table 3.  | Signal names                                                                 | 7   |

| Table 4.  | Instruction set for the M93C46                                               | 11  |

| Table 5.  | Instruction set for the M93C56 and M93C66                                    | 12  |

| Table 6.  | Instruction set for the M93C76 and M93C86                                    | 12  |

| Table 7.  | Absolute maximum ratings                                                     | 19  |

| Table 8.  | Operating conditions (M93Cx6)                                                | 20  |

| Table 9.  | Operating conditions (M93Cx6-W)                                              |     |

| Table 10. | Operating conditions (M93Cx6-R)                                              | 20  |

| Table 11. | AC measurement conditions (M93Cx6)                                           | 20  |

| Table 12. | AC measurement conditions (M93Cx6-W and M93Cx6-R)                            | 20  |

| Table 13. | Capacitance                                                                  | 21  |

| Table 14. | DC characteristics (M93Cx6, device grade 6)                                  | 21  |

| Table 15. | DC characteristics (M93Cx6-W, device grade 6)                                | 22  |

| Table 16. | DC characteristics (M93Cx6-R)                                                | 22  |

| Table 17. | AC characteristics (M93Cx6, device grade 6)                                  | 23  |

| Table 18. | AC characteristics (M93Cx6-W, device grade 6)                                | 24  |

| Table 19. | AC characteristics (M93Cx6-R)                                                | 25  |

| Table 20. | PDIP8 – 8 lead plastic dual in-line package, 300 mils body width,            |     |

|           | package mechanical data                                                      | 27  |

| Table 21. | SO8 narrow – 8 lead plastic small outline, 150 mils body width, package data | 28  |

| Table 22. | UFDFPN8 8-lead ultra thin fine pitch dual flat package no lead               |     |

|           | 2 x 3 mm, data                                                               | 29  |

| Table 23. | TSSOP8 – 8 lead thin shrink small outline, package mechanical data           | 30  |

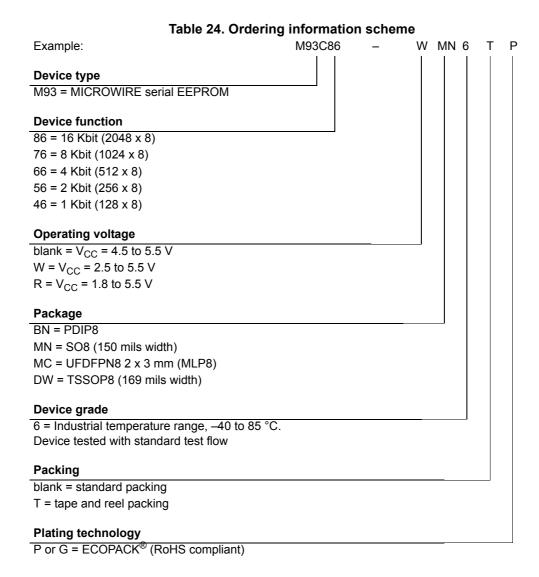

| Table 24. | Ordering information scheme                                                  |     |

| Table 25  | Document revision history                                                    | 3.2 |

4/33 DocID4997 Rev 13

# List of figures

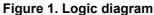

| Figure 1.  | Logic diagram                                                     | 6  |

|------------|-------------------------------------------------------------------|----|

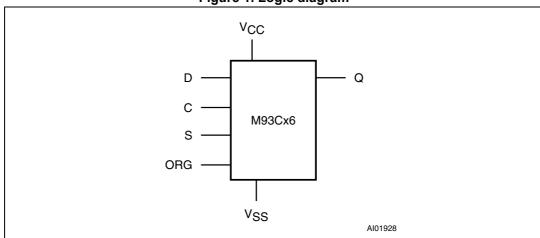

| Figure 2.  | 8-pin package connections (top view)                              |    |

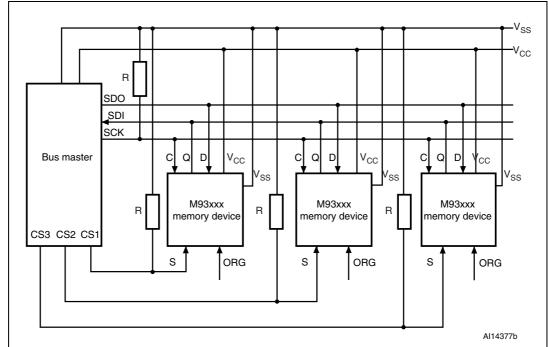

| Figure 3.  | Bus master and memory devices on the serial bus                   | 8  |

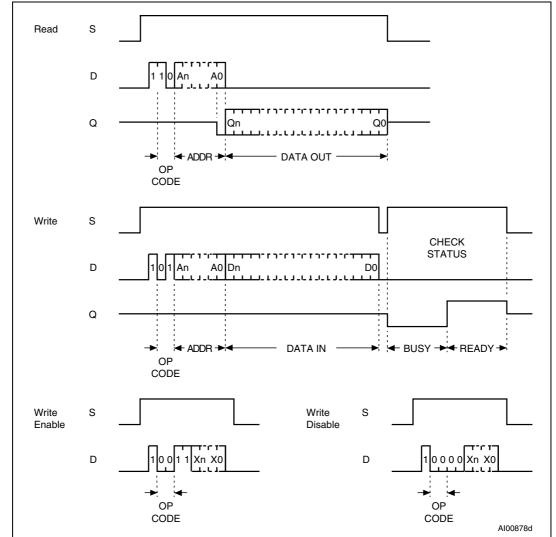

| Figure 4.  | READ, WRITE, WEN, WDS sequences                                   | 14 |

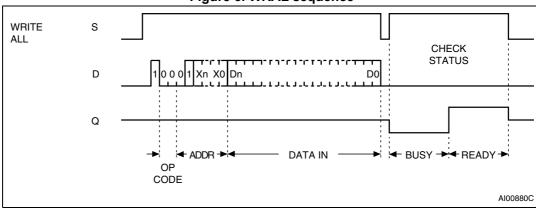

| Figure 5.  | WRAL sequence                                                     | 15 |

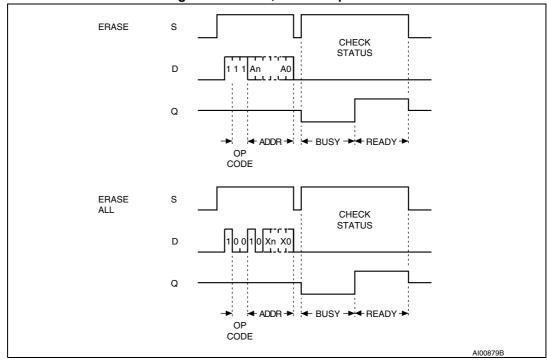

| Figure 6.  | ERASE, ERAL sequences                                             | 16 |

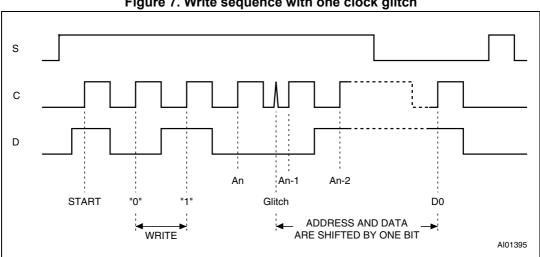

| Figure 7.  | Write sequence with one clock glitch                              | 18 |

| Figure 8.  | AC testing input output waveforms                                 | 21 |

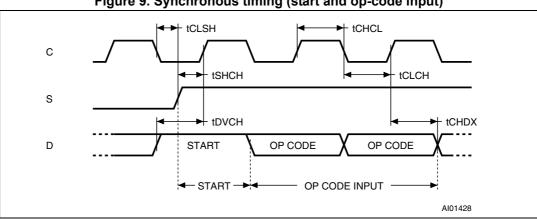

| Figure 9.  | Synchronous timing (start and op-code input)                      | 25 |

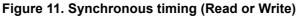

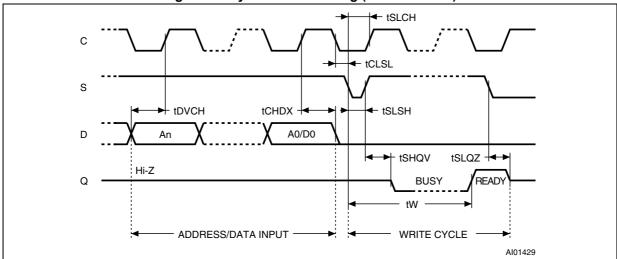

| Figure 10. | Synchronous timing (Read or Write)                                | 26 |

| Figure 11. | Synchronous timing (Read or Write)                                | 26 |

| Figure 12. | PDIP8 – 8 lead plastic dual in-line package, 300 mils body width, |    |

|            | package outline                                                   | 27 |

| Figure 13. | SO8 narrow – 8 lead plastic small outline, 150 mils body width,   |    |

|            | package outline                                                   | 28 |

| Figure 14. | UFDFPN8 8-lead ultra thin fine pitch dual flat package no lead    |    |

|            | 2 x 3 mm, outline                                                 | 29 |

| Figure 15. | TSSOP8 – 8 lead thin shrink small outline, package outline        | 30 |

# 1 Description

The M93C46 (1 Kbit), M93C56 (2 Kbit), M93C66 (4 Kbit), M93C76 (8 Kbit) and M93C86 (16 Kbit) are Electrically Erasable PROgrammable Memory (EEPROM) devices accessed through the MICROWIRE bus protocol. The memory array can be configured either in bytes (x8b) or in words (x16b).

The M93Cx6 devices operate within a voltage supply range from 4.5 V to 5.5 V, the M93Cx6-W devices operate within a voltage supply range from 2.5 V to 5.5 V, and the M93Cx6-R devices operate within a voltage supply range from 1.8 V to 5.5 V. All these devices operate with a clock frequency of 2 MHz (or less), over an ambient temperature range of -40  $^{\circ}$ C / +85  $^{\circ}$ C.

**Number of bits** Number of 8-bit bytes Number of 16-bit words **Device** M93C86 16384 2048 1024 M93C76 8192 1024 512 M93C66 4096 512 256 M93C56 2048 256 128 1024 128 64 M93C46

Table 2. Memory size versus organization

Table 3. Signal names

| Signal name     | Function            | Direction |

|-----------------|---------------------|-----------|

| S               | Chip Select         | Input     |

| D               | Serial Data input   | Input     |

| Q               | Serial Data output  | Output    |

| С               | Serial Clock        | Input     |

| ORG             | Organization Select | Input     |

| V <sub>CC</sub> | Supply voltage      |           |

| V <sub>SS</sub> | Ground              |           |

Figure 2. 8-pin package connections (top view)

- 1. See Section 11: Package mechanical data for package dimensions, and how to identify pin-1.

- DU = Don't Use. The DU (do not use) pin does not contribute to the normal operation of the device. It is

reserved for use by STMicroelectronics during test sequences. The pin may be left unconnected or may be

connected to V<sub>CC</sub> or V<sub>SS</sub>.

# 2 Connecting to the serial bus

*Figure 3* shows an example of three memory devices connected to an MCU, on a serial bus. Only one device is selected at a time, so only one device drives the Serial Data output (Q) line at a time, the other devices are high impedance.

The pull-down resistor R (represented in *Figure 3*) ensures that no device is selected if the bus master leaves the S line in the high impedance state.

In applications where the bus master may be in a state where all inputs/outputs are high impedance at the same time (for example, if the bus master is reset during the transmission of an instruction), the clock line (C) must be connected to an external pull-down resistor so that, if all inputs/outputs become high impedance, the C line is pulled low (while the S line is pulled low): this ensures that C does not become high at the same time as S goes low, and so, that the  $t_{\rm SI\ CH}$  requirement is met. The typical value of R is 100 k $\Omega$ .

Figure 3. Bus master and memory devices on the serial bus

8/33 DocID4997 Rev 13

# 3 Operating features

### 3.1 Supply voltage (V<sub>CC</sub>)

### 3.1.1 Operating supply voltage (V<sub>CC</sub>)

Prior to selecting the memory and issuing instructions to it, a valid and stable  $V_{CC}$  voltage within the specified [ $V_{CC}$ (min),  $V_{CC}$ (max)] range must be applied. In order to secure a stable DC supply voltage, it is recommended to decouple the  $V_{CC}$  line with a suitable capacitor (usually of the order of 10 nF to 100 nF) close to the  $V_{CC}/V_{SS}$  package pins.

This voltage must remain stable and valid until the end of the transmission of the instruction and, for a Write instruction, until the completion of the internal write cycle (t<sub>w</sub>).

### 3.1.2 Power-up conditions

When the power supply is turned on,  $V_{CC}$  rises from  $V_{SS}$  to  $V_{CC}$ . During this time, the Chip Select (S) line is not allowed to float and should be driven to  $V_{SS}$ , it is therefore recommended to connect the S line to  $V_{SS}$  via a suitable pull-down resistor.

The V<sub>CC</sub> rise time must not vary faster than 1 V/µs.

### 3.1.3 Power-up and device reset

In order to prevent inadvertent Write operations during power-up, a power on reset (POR) circuit is included. At power-up (continuous rise of  $V_{CC}$ ), the device does not respond to any instruction until  $V_{CC}$  has reached the power on reset threshold voltage (this threshold is lower than the minimum  $V_{CC}$  operating voltage defined in Operating conditions, in Section 10: DC and AC parameters).

When  $V_{CC}$  passes the POR threshold, the device is reset and is in the following state:

- Standby Power mode

- deselected (assuming that there is a pull-down resistor on the S line)

### 3.1.4 Power-down

At power-down (continuous decrease in  $V_{CC}$ ), as soon as  $V_{CC}$  drops from the normal operating voltage to below the power on reset threshold voltage, the device stops responding to any instruction sent to it.

During power-down, the device must be deselected and in the Standby Power mode (that is, there should be no internal Write cycle in progress).

# 4 Memory organization

The M93Cx6 memory is organized either as bytes (x8) or as words (x16). If Organization Select (ORG) is left unconnected (or connected to  $V_{CC}$ ) the x16 organization is selected; when Organization Select (ORG) is connected to Ground ( $V_{SS}$ ) the x8 organization is selected. When the M93Cx6 is in Standby mode, Organization Select (ORG) should be set either to  $V_{SS}$  or  $V_{CC}$  for minimum power consumption. Any voltage between  $V_{SS}$  and  $V_{CC}$  applied to Organization Select (ORG) may increase the Standby current.

10/33 DocID4997 Rev 13

### 5 Instructions

The instruction set of the M93Cx6 devices contains seven instructions, as summarized in *Table 4* to *Table 6*. Each instruction consists of the following parts, as shown in *Figure 4*: *READ, WRITE, WEN, WDS sequences*:

- Each instruction is preceded by a rising edge on Chip Select Input (S) with Serial Clock (C) being held low.

- A start bit, which is the first '1' read on Serial Data Input (D) during the rising edge of Serial Clock (C).

- Two op-code bits, read on Serial Data Input (D) during the rising edge of Serial Clock

(C). (Some instructions also use the first two bits of the address to define the op-code).

- The address bits of the byte or word that is to be accessed. For the M93C46, the address is made up of 6 bits for the x16 organization or 7 bits for the x8 organization (see *Table 4*). For the M93C56 and M93C66, the address is made up of 8 bits for the x16 organization or 9 bits for the x8 organization (see *Table 5*). For the M93C76 and M93C86, the address is made up of 10 bits for the x16 organization or 11 bits for the x8 organization (see *Table 6*).

The M93Cx6 devices are fabricated in CMOS technology and are therefore able to run as slow as 0 Hz (static input signals) or as fast as the maximum ratings specified in "AC characteristics" tables, in Section 10: DC and AC parameters.

x8 origination (ORG = 0) x16 origination (ORG = 1) Start Op-Instruction Description Required Required **Address** bit code Address Data clock Data clock (1) (1) cycles cycles Read Data from READ 1 10 A6-A0 Q7-Q0 A5-A0 Q15-Q0 Memory Write Data to **WRITE** 1 01 A6-A0 D7-D0 18 A5-A0 D15-D0 25 Memory 11X XXXX WEN Write Enable 1 00 10 11 XXXX 9 00X **WDS** Write Disable 1 00 10 00 XXXX 9 XXXX Erase Byte or **ERASE** 1 11 A6-A0 10 A5-A0 9 Word 10X **ERAL** Erase All Memory 1 00 10 10 XXXX 9 XXXX Write All Memory 01X **WRAL** 1 D7-D0 18 01 XXXX D15-D0 00 25 with same Data XXXX

Table 4. Instruction set for the M93C46

<sup>1.</sup> X = Don't Care bit.

| Table 5. Instruction set for the Mascad and Mascad |                                 |       |             |                          |       |                       |                           |        |                       |

|----------------------------------------------------|---------------------------------|-------|-------------|--------------------------|-------|-----------------------|---------------------------|--------|-----------------------|

|                                                    | Description                     | Start | Op-<br>code | x8 origination (ORG = 0) |       |                       | x16 origination (ORG = 1) |        |                       |

| Instruction                                        |                                 | bit   |             | Address<br>(1) (2)       | Data  | Required clock cycles | Address<br>(1) (3)        | Data   | Required clock cycles |

| READ                                               | Read Data from<br>Memory        | 1     | 10          | A8-A0                    | Q7-Q0 |                       | A7-A0                     | Q15-Q0 |                       |

| WRITE                                              | Write Data to<br>Memory         | 1     | 01          | A8-A0                    | D7-D0 | 20                    | A7-A0                     | D15-D0 | 27                    |

| WEN                                                | Write Enable                    | 1     | 00          | 1 1XXX<br>XXXX           |       | 12                    | 11XX<br>XXXX              |        | 11                    |

| WDS                                                | Write Disable                   | 1     | 00          | 0 0XXX<br>XXXX           |       | 12                    | 00XX<br>XXXX              |        | 11                    |

| ERASE                                              | Erase Byte or<br>Word           | 1     | 11          | A8-A0                    |       | 12                    | A7-A0                     |        | 11                    |

| ERAL                                               | Erase All<br>Memory             | 1     | 00          | 1 0XXX<br>XXXX           |       | 12                    | 10XX<br>XXXX              |        | 11                    |

| WRAL                                               | Write All Memory with same Data | 1     | 00          | 0 1XXX<br>XXXX           | D7-D0 | 20                    | 01XX<br>XXXX              | D15-D0 | 27                    |

Table 5. Instruction set for the M93C56 and M93C66

- 1. X = Don't Care bit.

- 2. Address bit A8 is not decoded by the M93C56.

- 3. Address bit A7 is not decoded by the M93C56.

Table 6. Instruction set for the M93C76 and M93C86

|             |                                 |              |             | x8 Origin               | x8 Origination (ORG = 0) |                       |                    | x16 Origination (ORG = 1) |                       |  |

|-------------|---------------------------------|--------------|-------------|-------------------------|--------------------------|-----------------------|--------------------|---------------------------|-----------------------|--|

| Instruction | Description                     | Start<br>bit | Op-<br>code | Address <sup>(1),</sup> | Data                     | Required clock cycles | Address<br>(1) (3) | Data                      | Required clock cycles |  |

| READ        | Read Data from<br>Memory        | 1            | 10          | A10-A0                  | Q7-Q0                    |                       | A9-A0              | Q15-Q0                    |                       |  |

| WRITE       | Write Data to<br>Memory         | 1            | 01          | A10-A0                  | D7-D0                    | 22                    | A9-A0              | D15-D0                    | 29                    |  |

| WEN         | Write Enable                    | 1            | 00          | 11X XXXX<br>XXXX        |                          | 14                    | 11 XXXX<br>XXXX    |                           | 13                    |  |

| WDS         | Write Disable                   | 1            | 00          | 00X XXXX<br>XXXX        |                          | 14                    | 00 XXXX<br>XXXX    |                           | 13                    |  |

| ERASE       | Erase Byte or Word              | 1            | 11          | A10-A0                  |                          | 14                    | A9-A0              |                           | 13                    |  |

| ERAL        | Erase All Memory                | 1            | 00          | 10X XXXX<br>XXXX        |                          | 14                    | 10 XXXX<br>XXXX    |                           | 13                    |  |

| WRAL        | Write All Memory with same Data | 1            | 00          | 01X XXXX<br>XXXX        | D7-D0                    | 22                    | 01 XXXX<br>XXXX    | D15-D0                    | 29                    |  |

- 1. X = Don't Care bit.

- 2. Address bit A10 is not decoded by the M93C76.

- 3. Address bit A9 is not decoded by the M93C76.

12/33 DocID4997 Rev 13

### 5.1 Read Data from Memory

The Read Data from Memory (READ) instruction outputs data on Serial Data Output (Q). When the instruction is received, the op-code and address are decoded, and the data from the memory is transferred to an output shift register. A dummy 0 bit is output first, followed by the 8-bit byte or 16-bit word, with the most significant bit first. Output data changes are triggered by the rising edge of Serial Clock (C). The M93Cx6 automatically increments the internal address register and clocks out the next byte (or word) as long as the Chip Select Input (S) is held High. In this case, the dummy 0 bit is *not* output between bytes (or words) and a continuous stream of data can be read (the address counter automatically rolls over to 00h when the highest address is reached).

### 5.2 Erase and Write data

### 5.2.1 Write Enable and Write Disable

The Write Enable (WEN) instruction enables the future execution of erase or write instructions, and the Write Disable (WDS) instruction disables it. When power is first applied, the M93Cx6 initializes itself so that erase and write instructions are disabled. After a Write Enable (WEN) instruction has been executed, erasing and writing remains enabled until a Write Disable (WDS) instruction is executed, or until  $V_{CC}$  falls below the power-on reset threshold voltage. To protect the memory contents from accidental corruption, it is advisable to issue the Write Disable (WDS) instruction after every write cycle. The Read Data from Memory (READ) instruction is not affected by the Write Enable (WEN) or Write Disable (WDS) instructions.

### 5.2.2 Write

For the Write Data to Memory (WRITE) instruction, 8 or 16 data bits follow the op-code and address bits. These form the byte or word that is to be written. As with the other bits, Serial Data Input (D) is sampled on the rising edge of Serial Clock (C).

After the last data bit has been sampled, the Chip Select Input (S) must be taken low before the next rising edge of Serial Clock (C). If Chip Select Input (S) is brought low before or after this specific time frame, the self-timed programming cycle will not be started, and the addressed location will not be programmed. The completion of the cycle can be detected by monitoring the READY/BUSY line, as described later in this document.

Once the Write cycle has been started, it is internally self-timed (the external clock signal on Serial Clock (C) may be stopped or left running after the start of a Write cycle). The Write cycle is automatically preceded by an Erase cycle, so it is unnecessary to execute an explicit erase instruction before a Write Data to Memory (WRITE) instruction.

Figure 4. READ, WRITE, WEN, WDS sequences

1. For the meanings of An, Xn, Qn and Dn, see *Table 4*, *Table 5* and *Table 6*.

### 5.2.3 Write All

As with the Erase All Memory (ERAL) instruction, the format of the Write All Memory with same Data (WRAL) instruction requires that a dummy address be provided. As with the Write Data to Memory (WRITE) instruction, the format of the Write All Memory with same Data (WRAL) instruction requires that an 8-bit data byte, or 16-bit data word, be provided. This value is written to all the addresses of the memory device. The completion of the cycle can be detected by monitoring the READY/BUSY line, as described next.

Figure 5. WRAL sequence

1. For the meanings of Xn and Dn, please see Table 4, Table 5 and Table 6.

### 5.2.4 Erase Byte or Word

The Erase Byte or Word (ERASE) instruction sets the bits of the addressed memory byte (or word) to 1. Once the address has been correctly decoded, the falling edge of the Chip Select Input (S) starts the self-timed <a href="Erase">Erase</a> cycle. The completion of the cycle can be detected by monitoring the READY/BUSY line, as described in <a href="Section 6: READY/BUSY">Section 6: READY/BUSY</a> status.

Figure 6. ERASE, ERAL sequences

1. For the meanings of An and Xn, please see Table 4, Table 5 and Table 6.

### 5.2.5 Erase All

The Erase All Memory (ERAL) instruction erases the whole memory (all memory bits are set to 1). The format of the instruction requires that a dummy address be provided. The Erase cycle is conducted in the same way as the Erase instruction (ERASE). The completion of the cycle can be detected by monitoring the READY/BUSY line, as described in Section 6: READY/BUSY status.

16/33 DocID4997 Rev 13

# 6 READY/BUSY status

While the Write or Erase cycle is underway, for a WRITE, ERASE, WRAL or ERAL instruction, the Busy signal (Q=0) is returned whenever Chip Select input (S) is driven high. (Please note, though, that there is an initial delay, of  $t_{SLSH}$ , before this status information becomes available). In this state, the M93Cx6 ignores any data on the bus. When the Write cycle is completed, and Chip Select Input (S) is driven high, the Ready signal (Q=1) indicates that the M93Cx6 is ready to receive the next instruction. Serial Data Output (Q) remains set to 1 until the Chip Select Input (S) is brought low or until a new start bit is decoded.

# 7 Initial delivery state

The device is delivered with all bits in the memory array set to 1 (each byte contains FFh).

#### **Clock pulse counter** 8

In a noisy environment, the number of pulses received on Serial Clock (C) may be greater than the number delivered by the master (the microcontroller). This can lead to a misalignment of the instruction of one or more bits (as shown in Figure 7) and may lead to the writing of erroneous data at an erroneous address.

To avoid this problem, the M93Cx6 has an on-chip counter that counts the clock pulses from the start bit until the falling edge of the Chip Select Input (S). If the number of clock pulses received is not the number expected, the WRITE, ERASE, ERAL or WRAL instruction is aborted, and the contents of the memory are not modified.

The number of clock cycles expected for each instruction, and for each member of the M93Cx6 family, are summarized in Table 4: Instruction set for the M93C46 to Table 6: Instruction set for the M93C76 and M93C86. For example, a Write Data to Memory (WRITE) instruction on the M93C56 (or M93C66) expects 20 clock cycles (for the x8 organization) from the start bit to the falling edge of Chip Select Input (S). That is:

- 1 Start bit

- + 2 Op-code bits

- + 9 Address bits

- + 8 Data bits

Figure 7. Write sequence with one clock glitch

DocID4997 Rev 13 18/33

# 9 Maximum rating

Stressing the device outside the ratings listed in the Absolute maximum ratings table may cause permanent damage to the device. These are stress ratings only, and operation of the device at these, or any other conditions outside those indicated in the operating sections of this specification, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 7. Absolute maximum ratings

| Symbol            | Parameter                                  |                                | Min.  | Max.                 | Unit |

|-------------------|--------------------------------------------|--------------------------------|-------|----------------------|------|

|                   | Ambient operating temperature              | <del>-4</del> 0                | 130   | °C                   |      |

| T <sub>STG</sub>  | Storage temperature                        | <del>-</del> 65                | 150   | °C                   |      |

| т                 | Load tomporature during soldering          | PDIP                           |       | 260 <sup>(1)</sup>   |      |

| T <sub>LEAD</sub> | Lead temperature during soldering          | other packages                 | See n | See note (2)         |      |

| V <sub>OUT</sub>  | Output range (Q = V <sub>OH</sub> or Hi-Z) |                                | -0.50 | V <sub>CC</sub> +0.5 | V    |

| V <sub>IN</sub>   | Input range                                |                                | -0.50 | V <sub>CC</sub> +1   | V    |

| V <sub>CC</sub>   | Supply voltage                             | -0.50                          | 6.5   | V                    |      |

| V <sub>ESD</sub>  | Electrostatic discharge voltage (hun       | nan body model) <sup>(3)</sup> |       | 4000                 | V    |

<sup>1.</sup> T<sub>LEAD</sub> max must *not* be applied for more than 10 s.

<sup>2.</sup> Compliant with JEDEC Std J-STD-020D (for small body, Sn-Pb or Pb-free assembly), the ST ECOPACK® 7191395 specification, and the European directive on Restrictions of Hazardous Substances (RoHS) 2011/65/EU.

<sup>3.</sup> Positive and negative pulses applied on pin pairs, according to the AEC-Q100-002 (compliant with JEDEC Std JESD22-A114, C1 = 100pF, R1 =  $1500\Omega$ , R2 =  $500\Omega$ ).

# 10 DC and AC parameters

This section summarizes the operating and measurement conditions, and the dc and ac characteristics of the device. The parameters in the dc and ac characteristic tables that follow are derived from tests performed under the measurement conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters.

Table 8. Operating conditions (M93Cx6)

| Symbol          | Parameter                     | Min. | Max. | Unit |

|-----------------|-------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                | 4.5  | 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature | -40  | 85   | °C   |

### Table 9. Operating conditions (M93Cx6-W)

| Symbol          | Parameter                     | Min. | Max. | Unit |

|-----------------|-------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                | 2.5  | 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature | -40  | 85   | °C   |

### Table 10. Operating conditions (M93Cx6-R)

| Symbol          | Parameter                     | Min. | Max. | Unit |

|-----------------|-------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                | 1.8  | 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature | -40  | 85   | °C   |

### Table 11. AC measurement conditions (M93Cx6)

| Symbol | Parameter                        | Min.            | Max. | Unit |

|--------|----------------------------------|-----------------|------|------|

| $C_L$  | Load capacitance                 | 100             |      | pF   |

|        | Input rise and fall times        |                 | 50   | ns   |

|        | Input voltage levels             | 0.4 V to 2.4 V  |      | V    |

|        | Input timing reference voltages  | 1.0 V and 2.0 V |      | V    |

|        | Output timing reference voltages | 0.8 V and 2.0 V |      | V    |

### Table 12. AC measurement conditions (M93Cx6-W and M93Cx6-R)

| Symbol | Parameter                        | Min.                                       | Max. | Unit |

|--------|----------------------------------|--------------------------------------------|------|------|

| $C_L$  | Load capacitance                 | 100                                        |      | pF   |

|        | Input rise and fall times        |                                            | 50   | ns   |

|        | Input voltage levels             | 0.2 V <sub>CC</sub> to 0.8 V <sub>CC</sub> |      | V    |

|        | Input timing reference voltages  | 0.3 V <sub>CC</sub> to 0.7 V <sub>CC</sub> |      | V    |

|        | Output timing reference voltages | 0.3 V <sub>CC</sub> to 0.7 V <sub>CC</sub> |      | V    |

20/33 DocID4997 Rev 13

M93CXX 2.4V 2.0V Input and output Input voltage levels timing reference levels 1V 0.4V Input Output M93CXX-W and M93CXX-R  $0.8V_{CC}$ -- 0.7V<sub>CC</sub> Input and output Input voltage levels timing reference levels 0.3V<sub>CC</sub>  $0.2V_{CC}$ MS19788V2

Figure 8. AC testing input output waveforms

Table 13. Capacitance

| Symbol           | Parameter          | Test condition <sup>(1)</sup> | Min | Max | Unit |

|------------------|--------------------|-------------------------------|-----|-----|------|

| C <sub>OUT</sub> | Output capacitance | V <sub>OUT</sub> = 0V         |     | 5   | pF   |

| C <sub>IN</sub>  | Input capacitance  | V <sub>IN</sub> = 0V          |     | 5   | pF   |

<sup>1.</sup> Sampled only, not 100% tested, at  $T_A$  = 25 °C and a frequency of 1 MHz.

Table 14. DC characteristics (M93Cx6, device grade 6)

| Symbol                         | Parameter                | Test condition                                                                                                      | Min.               | Max.                | Unit |

|--------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|------|

| I <sub>LI</sub>                | Input leakage current    | $0V \le V_{IN} \le V_{CC}$                                                                                          |                    | ±2.5                | μA   |

| I <sub>LO</sub>                | Output leakage current   | $0V \le V_{OUT} \le V_{CC}$ , Q in Hi-Z                                                                             |                    | ±2.5                | μA   |

| I <sub>CC</sub>                | Supply current           | $V_{CC}$ = 5 V, S = $V_{IH}$ , f = 2 MHz,<br>Q = open                                                               |                    | 2                   | mA   |

| I <sub>CC1</sub>               | Supply current (Standby) | $V_{CC}$ = 5 V, S = $V_{SS}$ , C = $V_{SS}$ ,<br>ORG = $V_{SS}$ or $V_{CC}$ ,<br>pin7 = $V_{CC}$ , $V_{SS}$ or Hi-Z |                    | 15                  | μA   |

| V <sub>IL</sub> <sup>(1)</sup> | Input low voltage        | $V_{CC} = 5 V \pm 10\%$                                                                                             | -0.45              | 0.8                 | V    |

| V <sub>IH</sub> <sup>(1)</sup> | Input high voltage       | $V_{CC} = 5 V \pm 10\%$                                                                                             | 2                  | V <sub>CC</sub> + 1 | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage       | $V_{CC} = 5 \text{ V}, I_{OL} = 2.1 \text{ mA}$                                                                     |                    | 0.4                 | V    |

| V <sub>OH</sub> <sup>(1)</sup> | Output high voltage      | V <sub>CC</sub> = 5 V, I <sub>OH</sub> = -400 μA                                                                    | 0.8V <sub>CC</sub> |                     | V    |

Please note that the input and output levels defined in this table are compatible with TTL logic levels and are NOT fully compatible with CMOS levels (as defined in *Table 15*).

47/

Table 15. DC characteristics (M93Cx6-W, device grade 6)

| Symbol           | Parameter                    | Test condition                                                                                                  | Min.                 | Max.                | Unit        |

|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------|---------------------|-------------|

| I <sub>LI</sub>  | Input leakage current        | $0V \le V_{IN} \le V_{CC}$                                                                                      |                      | ±2.5                | μA          |

| I <sub>LO</sub>  | Output leakage current       | $0V \le V_{OUT} \le V_{CC}$ , Q in Hi-Z                                                                         |                      | ±2.5                | μΑ          |

| laa              | Supply current (CMOS         | $V_{CC}$ = 5 V, S = $V_{IH}$ , f = 2 MHz,<br>Q = open                                                           |                      | 2                   | mA          |

| Icc              | inputs)                      | $V_{CC}$ = 2.5 V, S = $V_{IH}$ , f = 2 MHz,<br>Q = open                                                         |                      | 1                   | mA          |

| I <sub>CC1</sub> | Supply current (Standby)     | $V_{CC}$ = 2.5 V, S = $V_{SS}$ , C = $V_{SS}$ , ORG = $V_{SS}$ or $V_{CC}$ , pin7 = $V_{CC}$ , $V_{SS}$ or Hi-Z |                      | 5                   | μA          |

| $V_{IL}$         | Input low voltage (D, C, S)  |                                                                                                                 | -0.45                | 0.2 V <sub>CC</sub> | ٧           |

| V <sub>IH</sub>  | Input high voltage (D, C, S) |                                                                                                                 | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> + 1 | <b>&gt;</b> |

| W                | Output low voltage (O)       | $V_{CC}$ = 5 V, $I_{OL}$ = 2.1 mA                                                                               |                      | 0.4                 | ٧           |

| V <sub>OL</sub>  | Output low voltage (Q)       | $V_{CC}$ = 2.5 V, $I_{OL}$ = 100 $\mu$ A                                                                        |                      | 0.2                 | V           |

| V                | Output high voltage (Q)      | V <sub>CC</sub> = 5 V, I <sub>OH</sub> = -400 μA                                                                | 0.8 V <sub>CC</sub>  |                     | ٧           |

| V <sub>OH</sub>  | Output high voltage (Q)      | $V_{CC}$ = 2.5 V, $I_{OH}$ = -100 $\mu$ A                                                                       | V <sub>CC</sub> -0.2 |                     | V           |

Table 16. DC characteristics (M93Cx6-R)

| Symbol           | Parameter                    | Parameter Test condition                                                                                              |                      | Max. <sup>(1)</sup> | Unit |

|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|------|

| I <sub>LI</sub>  | Input leakage current        | $0V \leq V_{IN} \leq V_{CC}$                                                                                          |                      | ±2.5                | μΑ   |

| I <sub>LO</sub>  | Output leakage current       | $0V \le V_{OUT} \le V_{CC}$ , Q in Hi-Z                                                                               |                      | ±2.5                | μΑ   |

|                  | Supply current (CMOS         | $V_{CC}$ = 5 V, S = $V_{IH}$ , f = 2 MHz,<br>Q = open                                                                 |                      | 2                   | mA   |

| Icc              | inputs)                      | $V_{CC}$ = 1.8 V, S = $V_{IH}$ , f = 1 MHz,<br>Q = open                                                               |                      | 1                   | mA   |

| I <sub>CC1</sub> | Supply current (Standby)     | $V_{CC}$ = 1.8 V, S = $V_{SS}$ , C = $V_{SS}$ ,<br>ORG = $V_{SS}$ or $V_{CC}$ ,<br>pin7 = $V_{CC}$ , $V_{SS}$ or Hi-Z |                      | 2                   | μA   |

| V <sub>IL</sub>  | Input low voltage (D, C, S)  |                                                                                                                       | -0.45                | 0.2 V <sub>CC</sub> | V    |

| V <sub>IH</sub>  | Input high voltage (D, C, S) |                                                                                                                       | 0.8 V <sub>CC</sub>  | V <sub>CC</sub> + 1 | ٧    |

| V <sub>OL</sub>  | Output low voltage (Q)       | V <sub>CC</sub> = 1.8 V, I <sub>OL</sub> = 100 μA                                                                     |                      | 0.2                 | V    |

| V <sub>OH</sub>  | Output high voltage (Q)      | $V_{CC}$ = 1.8 V, $I_{OH}$ = -100 $\mu$ A                                                                             | V <sub>CC</sub> -0.2 |                     | V    |

This product is under development. For more information, please contact your nearest ST sales office.

Table 17. AC characteristics (M93Cx6, device grade 6)

|                                  | Test conditions specified in Table 8 and Table 11 |                                                  |                                  |      |      |  |  |

|----------------------------------|---------------------------------------------------|--------------------------------------------------|----------------------------------|------|------|--|--|

| Symbol                           | Alt.                                              | Parameter Min                                    |                                  | Max. | Unit |  |  |

| $f_{\mathbb{C}}$                 | $f_{SK}$                                          | Clock frequency                                  | D.C.                             | 2    | MHz  |  |  |

| t <sub>SLCH</sub>                |                                                   | Chip Select low to Clock high                    | 50                               |      | ns   |  |  |

|                                  |                                                   | Chip Select setup time<br>M93C46, M93C56, M93C66 | 50                               |      | ns   |  |  |

| t <sub>SHCH</sub>                | t <sub>CSS</sub>                                  | Chip Select setup time<br>M93C76, M93C86         | 50                               |      | ns   |  |  |

| t <sub>SLSH</sub> <sup>(1)</sup> | t <sub>CS</sub>                                   | Chip Select low to Chip Select high              |                                  |      | ns   |  |  |

| t <sub>CHCL</sub> <sup>(2)</sup> | t <sub>SKH</sub>                                  | Clock high time                                  | 200                              |      | ns   |  |  |

| t <sub>CLCH</sub> <sup>(2)</sup> | t <sub>SKL</sub>                                  | Clock low time                                   | 200                              |      | ns   |  |  |

| t <sub>DVCH</sub>                | t <sub>DIS</sub>                                  | Data in setup time                               | 50                               |      | ns   |  |  |

| t <sub>CHDX</sub>                | t <sub>DIH</sub>                                  | Data in hold time                                | 50                               |      | ns   |  |  |

| t <sub>CLSH</sub>                | t <sub>SKS</sub>                                  | Clock setup time (relative to S)                 | 50                               |      | ns   |  |  |

| t <sub>CLSL</sub>                | t <sub>CSH</sub>                                  | Chip Select hold time                            | 0                                |      | ns   |  |  |

| t <sub>SHQV</sub>                | t <sub>SV</sub>                                   | Chip Select to READY/BUSY status                 | Chip Select to READY/BUSY status |      | ns   |  |  |

| t <sub>SLQZ</sub>                | t <sub>DF</sub>                                   | Chip Select low to output Hi-Z                   |                                  | 100  | ns   |  |  |

| t <sub>CHQL</sub>                | t <sub>PD0</sub>                                  | Delay to output low                              |                                  | 200  | ns   |  |  |

| t <sub>CHQV</sub>                | t <sub>PD1</sub>                                  | Delay to output valid                            |                                  | 200  | ns   |  |  |

| t <sub>W</sub>                   | t <sub>WP</sub>                                   | Erase or Write cycle time                        |                                  | 5    | ms   |  |  |

Chip Select Input (S) must be brought low for a minimum of t<sub>SLSH</sub> between consecutive instruction cycles.

<sup>2.</sup>  $t_{CHCL} + t_{CLCH} \ge 1 / f_C$ .

Table 18. AC characteristics (M93Cx6-W, device grade 6)

|                                  | Test conditions specified in Table 9 and Table 12 |                                     |      |      |      |  |  |

|----------------------------------|---------------------------------------------------|-------------------------------------|------|------|------|--|--|

| Symbol                           | Alt.                                              | Parameter                           | Min. | Max. | Unit |  |  |

| f <sub>C</sub>                   | $f_{SK}$                                          | Clock frequency                     | D.C. | 2    | MHz  |  |  |

| t <sub>SLCH</sub>                |                                                   | Chip Select low to Clock high       | 50   |      | ns   |  |  |

| t <sub>SHCH</sub>                | t <sub>CSS</sub>                                  | Chip Select setup time              | 50   |      | ns   |  |  |

| t <sub>SLSH</sub> <sup>(1)</sup> | t <sub>CS</sub>                                   | Chip Select low to Chip Select high | 200  |      | ns   |  |  |

| t <sub>CHCL</sub> <sup>(2)</sup> | t <sub>SKH</sub>                                  | Clock high time                     | 200  |      | ns   |  |  |

| t <sub>CLCH</sub> <sup>(2)</sup> | t <sub>SKL</sub>                                  | Clock low time                      | 200  |      | ns   |  |  |

| t <sub>DVCH</sub>                | t <sub>DIS</sub>                                  | Data in setup time                  | 50   |      | ns   |  |  |

| t <sub>CHDX</sub>                | t <sub>DIH</sub>                                  | Data in hold time                   | 50   |      | ns   |  |  |

| t <sub>CLSH</sub>                | t <sub>SKS</sub>                                  | Clock setup time (relative to S)    | 50   |      | ns   |  |  |

| t <sub>CLSL</sub>                | t <sub>CSH</sub>                                  | Chip Select hold time               | 0    |      | ns   |  |  |

| t <sub>SHQV</sub>                | t <sub>SV</sub>                                   | Chip Select to READY/BUSY status    |      | 200  | ns   |  |  |

| t <sub>SLQZ</sub>                | t <sub>DF</sub>                                   | Chip Select low to output Hi-Z      |      | 100  | ns   |  |  |

| t <sub>CHQL</sub>                | t <sub>PD0</sub>                                  | Delay to output low                 |      | 200  | ns   |  |  |

| t <sub>CHQV</sub>                | t <sub>PD1</sub>                                  | Delay to output valid               |      | 200  | ns   |  |  |

| t <sub>W</sub>                   | t <sub>WP</sub>                                   | Erase or Write cycle time           |      | 5    | ms   |  |  |

Chip Select Input (S) must be brought low for a minimum of t<sub>SLSH</sub> between consecutive instruction cycles.

<sup>2.</sup>  $t_{CHCL}$  +  $t_{CLCH} \ge 1 / f_{C}$ .

Test conditions specified in Table 10 and Table 12 Min.<sup>(1)</sup> Max.<sup>(1)</sup> Unit **Symbol** Alt. **Parameter** D.C. 1  $\mathsf{MHz}$  $f_{C}$  $f_{SK}$ Clock frequency Chip Select low to Clock high 250 ns t<sub>SLCH</sub> Chip Select setup time 50 t<sub>SHCH</sub>  $t_{CSS}$ ns t<sub>SLSH</sub><sup>(2)</sup> Chip Select low to Chip Select high 250  $t_{CS}$ ns t<sub>CHCL</sub>(3) 250 Clock high time  $t_{SKH}$ ns  $t_{CLCH}^{(3)}$ 250 Clock low time t<sub>SKL</sub> ns 100 t<sub>DVCH</sub>  $t_{DIS}$ Data in setup time ns Data in hold time 100 t<sub>CHDX</sub>  $t_{DIH}$ Clock setup time (relative to S) 100 t<sub>CLSH</sub> t<sub>SKS</sub> ns Chip Select hold time ns t<sub>CLSL</sub> t<sub>CSH</sub> Chip Select to READY/BUSY status 400  $t_{SV}$ t<sub>SHQV</sub> Chip Select low to output Hi-Z 200  $t_{SLQZ}$  $t_{DF}$ ns Delay to output low 400 ns t<sub>CHQL</sub>  $t_{PD0}$ Delay to output valid 400 ns  $t_{CHQV}$  $t_{PD1}$ Erase or Write cycle time 10 ms  $t_{WP}$ t<sub>W</sub>

Table 19. AC characteristics (M93Cx6-R)

- This product is under development. For more information, please contact your nearest ST sales office.

- 2. Chip Select Input (S) must be brought low for a minimum of t<sub>SLSH</sub> between consecutive instruction cycles.

- 3.  $t_{CHCL} + t_{CLCH} \ge 1 / f_C$ .

Figure 9. Synchronous timing (start and op-code input)

С **←** tCLSL S → tDVCH tCHDX + → tCHQV ◆ tSLSH An A0 tSLQZ tCHQL → Hi-Z Q15/Q7 Q0 Q ADDRESS INPUT -- DATA OUTPUT -AI00820C

Figure 10. Synchronous timing (Read or Write)

## 11 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK® is an ST trademark .

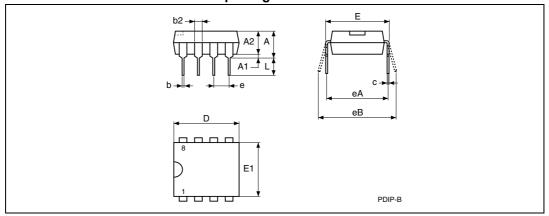

Figure 12. PDIP8 – 8 lead plastic dual in-line package, 300 mils body width, package outline

1. Drawing is not to scale.

Table 20. PDIP8 – 8 lead plastic dual in-line package, 300 mils body width, package mechanical data

| Compleal |      | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|----------|------|-------------|-------|--------|-----------------------|--------|--|

| Symbol   | Тур. | Min.        | Max.  | Тур.   | Min.                  | Max.   |  |

| А        | -    | -           | 5.33  | -      | -                     | 0.2098 |  |

| A1       | -    | 0.38        | -     | -      | 0.015                 | -      |  |

| A2       | 3.3  | 2.92        | 4.95  | 0.1299 | 0.115                 | 0.1949 |  |

| b        | 0.46 | 0.36        | 0.56  | 0.0181 | 0.0142                | 0.022  |  |

| b2       | 1.52 | 1.14        | 1.78  | 0.0598 | 0.0449                | 0.0701 |  |

| С        | 0.25 | 0.2         | 0.36  | 0.0098 | 0.0079                | 0.0142 |  |

| D        | 9.27 | 9.02        | 10.16 | 0.365  | 0.3551                | 0.4    |  |

| Е        | 7.87 | 7.62        | 8.26  | 0.3098 | 0.3                   | 0.3252 |  |

| E1       | 6.35 | 6.1         | 7.11  | 0.25   | 0.2402                | 0.2799 |  |

| е        | 2.54 | -           | -     | 0.1    | -                     | -      |  |

| eA       | 7.62 | -           | -     | 0.3    | -                     | -      |  |

| eВ       | -    | -           | 10.92 | -      | -                     | 0.4299 |  |

| L        | 3.3  | 2.92        | 3.81  | 0.1299 | 0.115                 | 0.15   |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

A2 D CCC O C

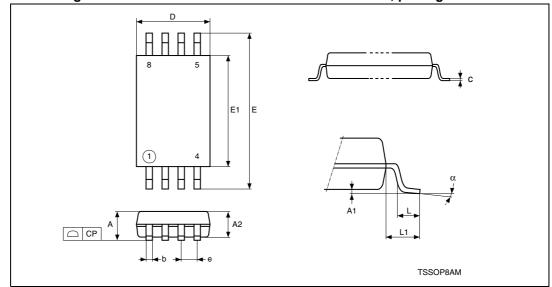

Figure 13. SO8 narrow – 8 lead plastic small outline, 150 mils body width, package outline

1. Drawing is not to scale.

Table 21. SO8 narrow - 8 lead plastic small outline, 150 mils body width, package data

| Symbol |      | millimeters |      |        | inches <sup>(1)</sup> |        |

|--------|------|-------------|------|--------|-----------------------|--------|

| Symbol | Тур  | Min         | Max  | Тур    | Min                   | Max    |

| А      | -    | -           | 1.75 | -      | -                     | 0.0689 |

| A1     | -    | 0.1         | 0.25 | -      | 0.0039                | 0.0098 |

| A2     | -    | 1.25        | -    | -      | 0.0492                | -      |

| b      | -    | 0.28        | 0.48 | -      | 0.011                 | 0.0189 |

| С      | -    | 0.17        | 0.23 | -      | 0.0067                | 0.0091 |

| ccc    | -    | -           | 0.1  | -      | -                     | 0.0039 |

| D      | 4.9  | 4.8         | 5    | 0.1929 | 0.189                 | 0.1969 |

| Е      | 6    | 5.8         | 6.2  | 0.2362 | 0.2283                | 0.2441 |

| E1     | 3.9  | 3.8         | 4    | 0.1535 | 0.1496                | 0.1575 |

| е      | 1.27 | -           | -    | 0.05   | -                     | -      |

| h      | -    | 0.25        | 0.5  | -      | 0.0098                | 0.0197 |

| k      | -    | 0°          | 8°   | -      | 0°                    | 8°     |

| L      | -    | 0.4         | 1.27 | -      | 0.0157                | 0.05   |

| L1     | 1.04 | -           | -    | 0.0409 | -                     | -      |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

Pin 1 E2

ZW\_MEeV2

Figure 14. UFDFPN8 8-lead ultra thin fine pitch dual flat package no lead 2 x 3 mm, outline

- 1. Drawing is not to scale.