EPF10K30ATC144-1 FPGA: คุณสมบัติแอปพลิเคชันการเขียนโปรแกรมและทางเลือกที่อธิบาย

คู่มือนี้เกี่ยวกับ EPF10K30ATC144-1 ซึ่งเป็นชิป FPGA ประเภทหนึ่งมันอธิบายว่าชิปคืออะไรวิธีการทำงานและสถานที่ที่สามารถใช้งานได้คุณจะได้เรียนรู้เกี่ยวกับคุณสมบัติหลักเช่นหน่วยความจำในตัวบล็อกตรรกะที่ยืดหยุ่นและรองรับทั้งระบบ 3.3V และ 5Vนอกจากนี้ยังแสดงวิธีการใช้ชิปในโครงการเช่นระบบเสียง/วิดีโอเครื่องจักรอุตสาหกรรมและอุปกรณ์การแพทย์ซึ่งรวมถึงคำแนะนำการตั้งค่าทีละขั้นตอนการเปรียบเทียบชิ้นส่วนและเครื่องมือออกแบบเพื่อช่วยให้คุณเข้าใจและทำงานกับ FPGA นี้ได้อย่างง่ายดายแคตตาล็อก

EPF10K30ATC144-1 คืออะไร?

ที่ EPF10K30ATC144-1 เป็นสมาชิกของตระกูล FLEX10K FPGA ที่ออกแบบมาเพื่อส่งมอบตรรกะที่ตั้งโปรแกรมได้ด้วยความซับซ้อนปานกลางและความยืดหยุ่นสูงสร้างขึ้นโดยใช้เทคโนโลยี CMOS SRAM 0.3 ไมครอนอุปกรณ์นี้รองรับประตูที่ใช้งานได้ประมาณ 30,000 ประตูและรวมถึงองค์ประกอบตรรกะ 1,728 รายการที่จัดอยู่ในบล็อกอาร์เรย์ลอจิก (ห้องปฏิบัติการ)มันทำงานที่ 3.3Vรุ่นความเร็ว –1 ให้การทำงานที่ค่อนข้างรวดเร็วโดยมีความถี่หลักสูงถึงประมาณ 166 MHzอุปกรณ์รวมบล็อกอาร์เรย์แบบฝังตัว (EABS) สำหรับหน่วยความจำบนชิปซึ่งช่วยเพิ่มการจัดการข้อมูลและการควบคุมการทำงานในการออกแบบแบบฝังใช้กันอย่างแพร่หลายในการควบคุมอุตสาหกรรมการสื่อสารและระบบฝังตัวแบบดั้งเดิมมันให้บริการโซลูชันที่ตั้งโปรแกรมได้พร้อมการสนับสนุน I/O ที่แข็งแกร่งและความสามารถในการตรรกะที่เพียงพอสำหรับแอพพลิเคชั่นระดับกลางที่หลากหลายตระกูล Flex10K เป็นหนึ่งในสาย FPGA แรกที่รวมตรรกะที่ใช้ SRAM และบล็อก RAM แบบฝังตัวซึ่งให้ตัวเลือกที่ปรับขนาดได้ตั้งแต่ 10K ถึงมากกว่า 200K Gates System Gatesด้วย I/OS ที่เข้ากันได้กับ TTL และบล็อกหน่วยความจำแบบฝังตัวอุปกรณ์ Flex10K นำเสนอการผสมผสานที่สมดุลของความหนาแน่นของตรรกะการรวมและประสิทธิภาพสำหรับระบบนิเวศการออกแบบที่เก่ากว่า

กำลังมองหา EPF10K30ATC144-1?ติดต่อเราเพื่อตรวจสอบหุ้นปัจจุบันเวลารอคอยและราคา

EPF10K30ATC144-1 CAD รุ่น

สัญลักษณ์ EPF10K30ATC144-1

EPF10K30ATC144-1 รอยเท้า

EPF10K30ATC144-1 3D รุ่น

คุณสมบัติ EPF10K30ATC144-1

- สถาปัตยกรรมที่มีความหนาแน่นสูง

EPF10K30ATC144-1 ถูกสร้างขึ้นโดยใช้สถาปัตยกรรม Flex 10K ของ Altera ซึ่งมีประตูระบบสูงถึง 69,000 ประตูและองค์ประกอบตรรกะ 1,728 (LES)องค์ประกอบตรรกะเหล่านี้ทำหน้าที่เป็นหน่วยการสร้างสำหรับการใช้ฟังก์ชั่นลอจิกและการออกแบบดิจิทัลความหนาแน่นของตรรกะสูงนี้รองรับระบบดิจิตอลที่ซับซ้อนปานกลางเช่นเครื่องจักรสถานะโปรเซสเซอร์ขนาดเล็กและตรรกะคอนโทรลเลอร์บนชิปเดียว

- บล็อกอาร์เรย์ฝังตัว (EAB)

อุปกรณ์นี้มีบล็อกอาร์เรย์แบบฝังตัวหลายตัวให้ RAM ประมาณ 12.3 กิโลบิตEAB แต่ละตัวมี 2,048 บิตที่สามารถกำหนดค่าเป็น RAM หรือ ROM รองรับความกว้างบิตได้ถึง 256 บล็อกเหล่านี้อนุญาตให้รวมหน่วยความจำที่รวดเร็วและยืดหยุ่นภายใน FPGA โดยไม่ต้องใช้องค์ประกอบตรรกะทำให้เหมาะสำหรับการบัฟเฟอร์ตารางค้นหาและการจัดเก็บข้อมูลขนาดเล็กภายในชิป

- ตรรกะตาม SRAM ที่กำหนดค่าใหม่ได้

EPF10K30ATC144-1 ใช้เทคโนโลยี SRAM สำหรับตรรกะที่ตั้งโปรแกรมได้ซึ่งหมายความว่าสามารถเขียนโปรแกรมได้ไม่ จำกัด จำนวนครั้งซึ่งมีค่าระหว่างการสร้างต้นแบบและการอัพเกรดระบบคุณสามารถทดสอบแก้ไขและตรวจสอบฟังก์ชั่นวงจรหลายครั้งก่อนการปรับใช้ขั้นสุดท้าย

- การดำเนินการหลัก 3.3V กับ I/O ที่ทนต่อ 5V

FPGA นี้ทำงานด้วยแหล่งจ่าย 3.3V สำหรับตรรกะภายใน แต่รองรับหมุด I/O ที่ทนต่อ 5Vความเข้ากันได้สองแรงดันไฟฟ้านี้ช่วยให้มั่นใจได้ว่าอุปกรณ์สามารถเชื่อมต่อกับส่วนประกอบ 5V แบบดั้งเดิมได้อย่างปลอดภัยในขณะที่ยังคงประสิทธิภาพพลังงานแรงดันต่ำที่ทันสมัยสำหรับฟังก์ชั่นหลักมันทำให้การออกแบบระบบแรงดันไฟฟ้าผสมง่ายขึ้นโดยไม่ต้องใช้ตัวเปลี่ยนระดับ

- ตอกย้ำความเร็วสูง

อุปกรณ์รองรับความถี่ในการใช้งานสูงถึง 166.67 MHz ทำให้สามารถประมวลผลข้อมูลที่รวดเร็วและการจัดการสัญญาณในแอปพลิเคชันที่สำคัญความถี่สูงสุดสูงนี้ทำให้ EPF10K30ATC144-1 เหมาะสำหรับระบบควบคุมความเร็วสูงการสื่อสารและงานคอมพิวเตอร์ที่ฝังตัว

- โหมดสแตนด์บายพลังงานต่ำ

FPGA มีการใช้พลังงานคงที่ต่ำโดยมีกระแสไฟสแตนด์บายน้อยกว่า 0.5 Maสิ่งนี้จะช่วยให้อุปกรณ์สามารถใช้ในแอปพลิเคชันที่ไวต่อพลังงานซึ่งต้องย่อให้กำลังใช้งานไม่ได้ใช้งานเช่นเครื่องมือพกพาหรือระบบที่มีโหมดประหยัดพลังงาน

- ช่วงอุณหภูมิเชิงพาณิชย์

ได้รับการจัดอันดับสำหรับช่วงอุณหภูมิ 0 ° C ถึง +70 ° C สภาพแวดล้อมเชิงพาณิชย์มาตรฐานที่เหมาะสมสิ่งนี้ทำให้มั่นใจได้ว่าการทำงานที่เชื่อถือได้ในสภาพภายในอาคารโดยทั่วไปโดยไม่ต้องใช้ข้อกำหนดอุณหภูมิระดับอุตสาหกรรม

ไดอะแกรมบล็อกอุปกรณ์ Flex 10K

แผนภาพแสดงถึงสถาปัตยกรรมภายในของอุปกรณ์ FLEX 10K FPGA โดยเฉพาะ EPF10K30ATC144-1ที่แกนกลางของอุปกรณ์คืออาร์เรย์แบบฝังซึ่งประกอบด้วยส่วนประกอบหลักสองประเภท: บล็อกอาร์เรย์ลอจิก (ห้องปฏิบัติการ) และบล็อกอาร์เรย์ฝังตัว (EABS)ห้องปฏิบัติการประกอบด้วยองค์ประกอบลอจิกหลายรายการ (LES) ที่จัดการฟังก์ชั่นตรรกะอเนกประสงค์ทั่วไปLE แต่ละตัวเชื่อมต่อผ่านการเชื่อมต่อระหว่างกันซึ่งช่วยให้มีการใช้ตรรกะที่ยืดหยุ่นภายในห้องปฏิบัติการ

รอบห้องแล็บคือบล็อกอาร์เรย์แบบฝัง (EABS) แสดงในสีน้ำเงินเข้มเหล่านี้เป็นบล็อกหน่วยความจำที่มีความหนาแน่นสูงที่ใช้สำหรับฟังก์ชั่นเช่น RAM หรือ ROM ทำให้สามารถประมวลผลข้อมูลแบบฝังตัวหรือบัฟเฟอร์โดยตรงภายในผ้า FPGAการเชื่อมต่อระหว่างคอลัมน์และแถวเปิดใช้งานการสื่อสารระหว่างห้องปฏิบัติการ EABS และองค์ประกอบ I/O (IOES) ที่วางไว้รอบ ๆ ปริมณฑลของชิปการเชื่อมต่อระหว่างกันเหล่านี้รองรับเส้นทางการกำหนดเส้นทางที่ซับซ้อนและมีความสำคัญสำหรับการไหลของข้อมูลในส่วนตรรกะที่แตกต่างกัน

IOE แต่ละตัวเชื่อมต่อตรรกะภายในกับพินภายนอกทำให้อุปกรณ์สามารถเชื่อมต่อกับส่วนประกอบของระบบอื่น ๆ ได้โครงสร้างเป็นแบบแยกส่วนและสมมาตรนำเสนอเลย์เอาต์ที่มีประสิทธิภาพสำหรับการกำหนดเส้นทางและความสามารถในการปรับขนาดใน EPF10K30ATC144-1 การจัดเรียงนี้ช่วยให้การผสมผสานที่สมดุลของตรรกะที่ตั้งโปรแกรมได้และหน่วยความจำฝังตัวซึ่งเหมาะสำหรับระบบดิจิตอลที่มีความซับซ้อนขนาดกลางที่ต้องการการจัดการข้อมูลที่รวดเร็วและการกำหนดค่าตรรกะที่ยืดหยุ่น

ข้อมูลจำเพาะ EPF10K30ATC144-1

|

พิมพ์ |

พารามิเตอร์ |

|

ผู้ผลิต |

Altera/Intel |

|

ชุด |

Flex-10ka® |

|

การบรรจุหีบห่อ |

จำนวนมาก |

|

สถานะชิ้นส่วน |

คล่องแคล่ว |

|

จำนวนห้องปฏิบัติการ/CLBS |

216 |

|

จำนวน I/O |

102 |

|

แรงดันไฟฟ้า - อุปทาน |

3V ~ 3.6V |

|

ประเภทการติดตั้ง |

ติดตั้งพื้นผิว |

|

อุณหภูมิการทำงาน |

0 ° C ~ 70 ° C (TA) |

|

แพ็คเกจ / เคส |

144-LQFP |

|

แพ็คเกจอุปกรณ์ซัพพลายเออร์ |

144-TQFP (20x20) |

|

หมายเลขผลิตภัณฑ์พื้นฐาน |

EPF10K30 |

แอปพลิเคชัน EPF10K30ATC144-1

การประมวลผลเสียง / วิดีโอดิจิตอล

EPF10K30ATC144-1 เหมาะสำหรับงานการประมวลผลเสียงและวิดีโอเนื่องจากบล็อกอาร์เรย์แบบฝังตัว (EABS) ที่ให้บริการ RAM บนชิปคุณสมบัตินี้ช่วยให้สามารถบัฟเฟอร์การจัดเก็บชั่วคราวและการจัดการข้อมูลโดยตรงภายใน FPGAหลายคนมักจะใช้ FPGA นี้เพื่อจัดการการถอดรหัสสตรีมเสียงการจัดการพิกเซลหรือช่วงเวลาอินเตอร์เฟสวิดีโอดิจิตอลความสามารถในการตรรกะปานกลางและความยืดหยุ่น I/O ช่วยให้การรวมเข้ากับตัวแปลงสัญญาณตัวควบคุมเวลาและตรรกะการซิงโครไนซ์ในระบบมัลติมีเดีย

ระบบควบคุมอุตสาหกรรม

ในระบบอัตโนมัติอุตสาหกรรม EPF10K30ATC144-1 สามารถทำหน้าที่เป็นตัวควบคุมกลางหรืออินเทอร์เฟซ I/O อัจฉริยะตรรกะที่ตั้งโปรแกรมได้รองรับการใช้งานเครื่องจักรของรัฐอินเทอร์เฟซเซ็นเซอร์การเก็บข้อมูลและโปรโตคอลการสื่อสารอนุกรมเช่น SPI หรือ RS-485ความพร้อมใช้งานของ RAM บนชิปและจำนวน I/O ที่มีขนาดใหญ่ทำให้เหมาะสำหรับการจัดการสัญญาณควบคุมหลายรายการในตัวควบคุมตรรกะที่ตั้งโปรแกรมได้ (PLCs) ไดรฟ์มอเตอร์หรือระบบย่อยหุ่นยนต์

อุปกรณ์การแพทย์

อุปกรณ์การแพทย์ต้องการตรรกะที่แม่นยำและกำหนดค่าใหม่เพื่อจัดการกับการไหลของข้อมูลพิเศษFPGA นี้สามารถใช้สำหรับการปรับสภาพสัญญาณการกรองและการประมวลผลอินพุตเซ็นเซอร์แบบอะนาล็อกในแอปพลิเคชันเช่น ECG, อัลตราซาวด์หรือระบบการถ่ายภาพเวลาแฝงที่คาดการณ์ได้และการเขียนโปรแกรมที่ยืดหยุ่นทำให้เหมาะสำหรับการบูรณาการอัลกอริทึมที่เป็นกรรมสิทธิ์หรือขั้นตอนการประมวลผลข้อมูลล่วงหน้าก่อนการจัดการไมโครคอนโทรลเลอร์หรือการจัดการ DSP เพิ่มเติม

อุปกรณ์อิเล็กทรอนิกส์ยานยนต์และการบินและอวกาศ

ในแดชบอร์ดยานยนต์, avionics, และหน่วยควบคุมการบินและอวกาศ, EPF10K30ATC144-1 มักใช้สำหรับการเชื่อมต่อเซ็นเซอร์การจัดการการวินิจฉัยหรือการใช้โปรโตคอลการสื่อสารลักษณะที่สามารถ reprogrammable ได้รับอนุญาตให้ปรับการปรับใช้ตรรกะหรือระหว่างการตรวจสอบความถูกต้องของระบบความยืดหยุ่นของ I/O ของชิ้นส่วนทำให้สามารถเชื่อมโยงระหว่างรถบัสรุ่นเก่าและระบบการสื่อสารที่ทันสมัยในขณะที่ยังคงความมั่นคงในสภาพแวดล้อมที่ทนทาน

ระบบการสื่อสารและเครือข่าย

ต้องขอบคุณความสามารถในการใช้งานโปรโตคอลอนุกรมและตรรกะการกรองข้อมูลที่กำหนดเอง EPF10K30ATC144-1 พบว่าใช้ในระบบโทรคมนาคมแบบดั้งเดิมและแบ็คแลนเครือข่ายRAM แบบฝังตัวรองรับการบัฟเฟอร์และการวิเคราะห์ส่วนหัวแพ็คเก็ตในขณะที่บล็อกตรรกะสามารถใช้กฎการสลับหรือการตรวจสอบความเท่าเทียมกันมันทำหน้าที่เป็นองค์ประกอบตรรกะกาวช่วยรวมโปรเซสเซอร์สวิตช์และเส้นทางสัญญาณในโครงสร้างพื้นฐานการสื่อสาร

EPF10K30ATC144-1 ชิ้นส่วนที่คล้ายกัน

EPF10K30AQI208-3 เป็นทางเลือกที่แข็งแกร่งสำหรับ EPF10K30ATC144-1 ซึ่งเสนอจำนวนองค์ประกอบลอจิกเดียวกัน (1,728 LES) และหน่วยความจำฝังตัว (~ 12.3 kbit) แต่มีแพ็คเกจ QFP 208 พินขนาดใหญ่มันเพิ่มจำนวนหมุด I/O ที่มีอยู่เป็น 147 ทำให้เหมาะสำหรับแอปพลิเคชันที่ต้องการการเชื่อมต่อภายนอกมากขึ้นด้วยคะแนนความเร็ว –3 ระดับอุตสาหกรรมมันทำงานได้อย่างน่าเชื่อถือในช่วงอุณหภูมิที่กว้างขึ้น –40 ° C ถึง +85 ° Cสิ่งนี้ทำให้เหมาะสำหรับสภาพแวดล้อมที่แข็งแกร่งในโทรคมนาคมระบบควบคุมและการติดตั้งอุตสาหกรรมที่ทนทานI/O ที่ขยายออกไปและช่วงการดำเนินงานทำให้เป็นการอัพเกรดที่ใช้งานได้จริงสำหรับการออกแบบที่เพิ่มขึ้นจากการกำหนดค่า TQFP 144 พิน

EPF10K30AQI240-3 เป็น FPGA ที่เข้ากันได้อีกตัวหนึ่งในตระกูล Flex 10K ซึ่งให้ความหนาแน่น I/O ที่สูงขึ้นพร้อมแพ็คเกจ QFP 240 พินและหมุด I/O 189เช่น ATC144-1 มันรักษาองค์ประกอบตรรกะ 1,728 และ 12.3 kbit ของ RAM ฝังตัวเกรดความเร็ว –3 ทำให้มั่นใจได้ว่าประสิทธิภาพที่สอดคล้องกันที่อุณหภูมิอุตสาหกรรมทำให้เป็นตัวเลือกที่เชื่อถือได้สำหรับระบบที่มีความผันผวนด้านสิ่งแวดล้อมในวงกว้างมันเหมาะสำหรับแอปพลิเคชันที่นับได้สูงเช่นแผงควบคุมที่ซับซ้อนระบบวิดีโอแบบฝังตัวและอินเทอร์เฟซการคำนวณแบบดั้งเดิม

EPF10K30AQC240-3 ยังมีหมุด 189 I/O ในเค้าโครง QFP 240 พินและรักษาสถาปัตยกรรมหลักของ 1,728 LES และ ~ 12 kbit ของ RAM บนชิปแม้ว่าตอนนี้จะแสดงให้เห็นว่าล้าสมัย แต่ก็ยังคงมีการเปลี่ยนที่ทำงานได้ในระบบที่จำเป็นต้องใช้รอยเท้าเชิงกลและ pinout สัญญาณของ QFP 240 พินมันมีหน้าที่เหมือนกับ AQI240-3 แต่โดยทั่วไปจะใช้ในการใช้งานอุณหภูมิเชิงพาณิชย์ส่วนนี้มีค่าสำหรับการบำรุงรักษาฮาร์ดแวร์แบบดั้งเดิมโดยเฉพาะอย่างยิ่งที่จำเป็นต้องใช้ความเข้ากันได้ทางกลแบบดรอปอินกับเค้าโครง 240 พินและการจัดหาการออกแบบใหม่ไม่สามารถทำได้

ขั้นตอนการเขียนโปรแกรม EPF10K30ATC144-1

1. สร้างและรวบรวมการออกแบบ

เริ่มต้นด้วยการออกแบบตรรกะดิจิตอลของคุณโดยใช้ HDL เช่น VHDL หรือ Verilogใช้เครื่องมือซอฟต์แวร์เช่น Altera Quartus II หรือ Max+Plus II เพื่อสร้างโครงการเมื่อการออกแบบของคุณเสร็จสมบูรณ์ให้รวบรวมเพื่อสร้างไฟล์การเขียนโปรแกรมคุณจะได้รับไฟล์. SOF สำหรับการกำหนดค่า JTAG ที่ใช้ SRAM และไฟล์. pof หากคุณต้องการตั้งโปรแกรม EEPROM อนุกรมสำหรับการโหลดแบบเปิดเครื่อง

2. เลือกวิธีการกำหนดค่า

มีสองวิธีหลักในการกำหนดค่า EPF10K30ATC144-1สำหรับการเขียนโปรแกรมชั่วคราวในระหว่างการทดสอบหรือพัฒนาให้ใช้การกำหนดค่า JTAG กับไฟล์. SOFสำหรับการกำหนดค่าถาวรหรืออัตโนมัติในการเริ่มต้นระบบให้ใช้วิธีการแบบพาสซีฟโดยการโหลดไฟล์. pof ลงใน EEPROM ภายนอก (เช่น EPC2)

3. เชื่อมต่อและตั้งโปรแกรมอุปกรณ์

หากใช้ JTAG ให้เชื่อมต่อสายเคเบิลโปรแกรม (เช่น USB-blaster) กับส่วนหัว JTAGเปิดโปรแกรมโปรแกรม Quartus โหลดไฟล์. sof และตั้งโปรแกรมอุปกรณ์โดยตรงสำหรับอนุกรมแบบพาสซีฟให้เชื่อมต่อ EEPROM กับ FPGA และใช้ Quartus เพื่อตั้งโปรแกรมไฟล์. pof ลงใน EEPROMด้วยการเพิ่มพลัง EEPROM จะส่งบิตสตรีมไปยัง FPGA

4. reprogram เมื่อจำเป็น

EPF10K30ATC144-1 สามารถ reprogrammed ได้ทุกเวลาผ่าน JTAGนอกจากนี้คุณยังสามารถอัปเดตเนื้อหา EEPROM เพื่อเปลี่ยนการกำหนดค่าเริ่มต้นสิ่งนี้มีประโยชน์สำหรับการอัปเดตฟิลด์หรือการปรับปรุงการออกแบบ

5. ตรวจสอบความสำเร็จในการเขียนโปรแกรม

หลังจากการเขียนโปรแกรมให้ตรวจสอบหมุดสถานะของ FPGA (NSTATUS และ CONF_DONE) เพื่อยืนยันการกำหนดค่าที่ประสบความสำเร็จนอกจากนี้คุณยังสามารถเรียกใช้การทดสอบการทำงานหรือใช้เครื่องมือการดีบักเช่น SignalTap เพื่อให้แน่ใจว่าลอจิกทำงานตามที่ตั้งใจไว้

EPF10K30ATC144-1 ข้อดี

- การรวมเข้ากับ RAM แบบฝังสูง

EPF10K30ATC144-1 รวมประตูระบบประมาณ 30,000 ประตูและองค์ประกอบตรรกะ 1,728 ตัวพร้อมกับ RAM ที่ฝังตัวประมาณ 12 กิโลกรัมบล็อกอาร์เรย์แบบฝังตัวเหล่านี้ (EABS) ช่วยให้การดำเนินการหน่วยความจำที่เร็วขึ้นและคาดการณ์ได้มากขึ้นเมื่อเทียบกับ RAM แบบกระจายสิ่งนี้จะช่วยให้การออกแบบตรรกะง่ายขึ้นโดยเฉพาะอย่างยิ่งในแอพพลิเคชั่นที่ต้องการบัฟเฟอร์ตารางการค้นหาหรือการจัดเก็บข้อมูลขนาดเล็กการปรับปรุงทั้งประสิทธิภาพและการใช้ทรัพยากร

- ความเข้ากันได้

หนึ่งในข้อได้เปรียบที่แข็งแกร่งของอุปกรณ์นี้คือความสามารถในการใช้งานกับการจัดหา 3.3V ในขณะที่รองรับ I/OS ที่ทนต่อ 5Vคุณลักษณะ Multivolt ™ I/O นี้ทำให้ FPGA มีความยืดหยุ่นสำหรับการรวมเข้ากับระบบที่ใช้ทั้งตรรกะ LEGACY 5V และส่วนประกอบ 3.3V ที่ทันสมัยมีประโยชน์ในระบบอุตสาหกรรมหรือการสื่อสารที่ระดับแรงดันไฟฟ้าแตกต่างกันไปตามระบบย่อย

- การกำหนดค่าใหม่ง่าย

เนื่องจากใช้เทคโนโลยี SRAM EPF10K30ATC144-1 สามารถ reprogrammed ได้อย่างง่ายดายโดยใช้ JTAG หรือวิธีการแบบพาสซีฟคุณสามารถอัปเดตฟังก์ชั่นลอจิกในฟิลด์หรือระหว่างการพัฒนาโดยไม่ต้องเปลี่ยนชิปสิ่งนี้จะช่วยลดต้นทุนและอนุญาตให้มีการอัพเกรดในอนาคตหรือแก้ไขข้อผิดพลาดหลังจากการปรับใช้

- JTAG ในตัวและการพัฒนาที่รวดเร็ว

อุปกรณ์ดังกล่าวรวมถึงการสนับสนุน JTAG ในตัวช่วยให้การทดสอบขอบเขตสแกนและการเขียนโปรแกรมในระบบสิ่งนี้มีค่าสำหรับการทดสอบการผลิตและการดีบักนอกจากนี้เมื่อเปรียบเทียบกับการพัฒนา ASIC แบบดั้งเดิมโดยใช้ FPGA นี้ช่วยลดเวลาการออกแบบอย่างมากทำให้เหมาะอย่างยิ่งสำหรับการสร้างต้นแบบอย่างรวดเร็วและการผลิตขนาดเล็กถึงระดับกลาง

- การกำหนดเส้นทางที่มีประสิทธิภาพและสถาปัตยกรรมประสิทธิภาพ

สถาปัตยกรรม Flex 10K ที่ใช้ในอุปกรณ์นี้รวมถึงการกำหนดเส้นทางFastTrack®, พกพาโซ่สำหรับตรรกะทางคณิตศาสตร์และต้นไม้นาฬิกาที่ทำให้มั่นใจได้ว่าเวลาที่คาดการณ์ได้และประสิทธิภาพที่มีประสิทธิภาพด้วยเกรดความเร็ว –1 ชิปสามารถทำงานได้สูงถึงประมาณ 166 MHz ซึ่งเหมาะสำหรับแอปพลิเคชันขนาดกลางจำนวนมากเช่นการควบคุมสัญญาณการจัดการข้อมูลและการเชื่อมต่อโปรโตคอล

EPF10K30ATC144-1 ขนาดบรรจุภัณฑ์

- ประเภทแพ็คเกจ: TQFP - 144 (แพ็คเกจแบนรูปสี่เหลี่ยมบาง ๆ , 144 พิน)

- การติดตั้ง: พื้นผิว

- ขนาดตัว: 20 มม. × 20 มม. (รวมถึงโอกาสในการขาย)

- พิทช์: 0.80 มม. (ระยะห่างระหว่างศูนย์พิน)

- ความยาวของร่างกาย (ไม่รวมโอกาสในการขาย): 12.00 มม. (เล็กน้อย)

- ความกว้างของร่างกาย (ไม่รวมโอกาสในการขาย): 12.00 มม. (เล็กน้อย)

- ความหนาโดยรวม: สูงถึง 1.20 มม.

- ความหนาของร่างกาย: ประมาณ 0.95 มม.

- ความยาวตะกั่ว: 0.45 มม. ถึง 0.75 มม.

- ความกว้างตะกั่ว: 0.30 มม. ถึง 0.45 มม.

- ความสูงของระนาบที่นั่ง (A1): 0.05 มม. ถึง 0.15 มม.

EPF10K30ATC144-1 ผู้ผลิต

EPF10K30ATC144-1 ผลิตโดย การเปลี่ยนแปลง ผู้บุกเบิกในอุปกรณ์ลอจิกที่ตั้งโปรแกรมได้และผู้พัฒนาดั้งเดิมของซีรี่ส์ Flex 10K FPGAก่อตั้งขึ้นในปีพ. ศ. 2526 Altera กลายเป็นผู้นำในนวัตกรรม Gate Array (FPGA) ที่ตั้งโปรแกรมได้ (FPGA) นวัตกรรมแนะนำวิธีแก้ปัญหาตรรกะที่ตั้งโปรแกรมได้เร็วที่สุดและใช้กันอย่างแพร่หลายที่สุดในอุตสาหกรรมในปี 2558 Altera ได้มาโดย Intel บริษัทซึ่งยังคงสนับสนุนและรวมสายผลิตภัณฑ์ FPGA ของ Altera ภายใต้กลุ่มโซลูชันที่ตั้งโปรแกรมได้ (PSG)แม้ว่า Altera จะเปิดตัวในปี 2567 ในฐานะ บริษัท ย่อย Intel แยกต่างหาก แต่ EPF10K30ATC144-1 ยังคงเป็น FPGA มรดกที่สะท้อนถึงความเป็นเลิศทางวิศวกรรมและการผลิตดั้งเดิมของ Altera

บทสรุป

EPF10K30ATC144-1 เป็นชิป FPGA ที่มีประโยชน์และยืดหยุ่นพร้อมหน่วยความจำที่ดีฟังก์ชั่นตรรกะที่แข็งแกร่งและความสามารถในการทำงานกับทั้งระบบใหม่และเก่าคุณสามารถ reprogram ได้ทุกที่ทุกเวลาซึ่งทำให้ดีสำหรับการทดสอบและการอัปเดตมันง่ายต่อการเชื่อมต่อและทำงานได้ดีในอุปกรณ์อิเล็กทรอนิกส์หลายประเภทตั้งแต่เครื่องจักรจากโรงงานไปจนถึงเครื่องมือเครือข่ายแม้ว่าจะเป็นส่วนที่เก่ากว่า แต่ก็ยังช่วยในหลายโครงการที่จำเป็นต้องใช้ชิปที่เชื่อถือได้และ reprogrammable

PDF แผ่นข้อมูล

EPF10K30ATC144-1 แผ่นข้อมูล:

เกี่ยวกับเรา

ALLELCO LIMITED

อ่านเพิ่มเติม

สอบถามรายละเอียดเพิ่มเติมอย่างรวดเร็ว

กรุณาส่งคำถามเราจะตอบกลับทันที

คำถามที่พบบ่อย [FAQ]

1. ฉันสามารถใช้ EPF10K30ATC144-1 ในระบบ 3.3V ที่ทันสมัยได้หรือไม่?

ใช่ EPF10K30ATC144-1 ทำงานที่ 3.3V และรองรับ I/O ที่ทนต่อ 5V ทำให้เข้ากันได้กับระบบแรงดันไฟฟ้าผสมทั้งใหม่และเก่า

2. ฉันต้องใช้ซอฟต์แวร์ใดในการตั้งโปรแกรม EPF10K30ATC144-1

คุณสามารถใช้เครื่องมือออกแบบมรดกของ Altera เช่น Quartus II หรือ Max+Plus II เพื่อสร้างและตั้งโปรแกรมไฟล์การออกแบบของคุณ (.sof และ. pof)

3. EPF10K30ATC144-1 เป็นตัวเลือกที่ดีสำหรับการสร้างต้นแบบหรือไม่?

ใช่ FPGA นี้เหมาะสำหรับการสร้างต้นแบบเนื่องจากตรรกะที่ใช้ SRAM ซึ่งช่วยให้การเขียนโปรแกรมแบบ reprogramming ไม่ จำกัด และการเปลี่ยนแปลงการออกแบบที่รวดเร็ว

4. EPF10K30ATC144-1 สนับสนุนการเขียนโปรแกรม JTAG หรือไม่?

ใช่รองรับการเขียนโปรแกรม JTAG เต็มรูปแบบและการสแกนขอบเขตทำให้สามารถกำหนดค่าและการทดสอบในระบบในระหว่างการพัฒนาหรือหลังการปรับใช้

5. ความถี่สูงสุดที่ EPF10K30ATC144-1 สามารถทำงานได้คืออะไร?

รองรับความเร็วสัญญาณนาฬิกาสูงถึงประมาณ 166 MHz ทำให้เหมาะสำหรับการประมวลผลสัญญาณที่รวดเร็วและงานที่สำคัญ

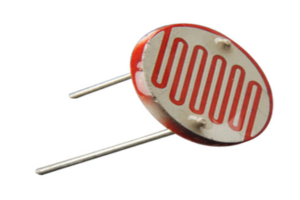

LDR คืออะไรและใช้งานได้อย่างไรในอุปกรณ์อิเล็กทรอนิกส์

บน 17/06/2025

ADG526AKRZ มัลติเพล็กเซอร์อะนาล็อก: คุณสมบัติ, pinout, แอปพลิเคชันและคู่มือการตั้งค่า

บน 17/06/2025

โพสต์ยอดนิยม

-

คอมพิวเตอร์ชุดคำสั่งที่ซับซ้อน: พวกเขาเปลี่ยนการคำนวณอย่างไร?

บน 18/04/8000 147771

-

USB-C Pinout และคุณสมบัติ

บน 18/04/2000 112007

-

การใช้ Xilinx Unified Simulation Primitives: คู่มือที่ครอบคลุมสำหรับการออกแบบและการจำลอง FPGA

บน 18/04/1600 111351

-

การทำความเข้าใจแรงดันไฟฟ้าของแหล่งจ่ายไฟในอิเล็กทรอนิกส์ VCC, VDD, VEE, VSS และ GND

บน 18/04/0400 83768

-

คู่มือเชื่อมต่อ RJ45: Pinout, การเดินสาย, ประเภทสายเคเบิลและการใช้งาน

บน 01/01/1970 79565

-

คู่มือที่ดีที่สุดสำหรับรหัสสีลวดในระบบไฟฟ้าที่ทันสมัย

วิธีที่ระบบไฟฟ้าของเราใช้สีไม่ได้มีไว้สำหรับรูปลักษณ์ตอนนี้สีลวดแต่ละอันบ่งบอกถึงฟังก์ชั่นเฉพาะทำให้ง่ายต่อการระบุและจัดการส่วนประกอบไฟฟ้าอย่างถูกต้องระหว่างการติดตั้งและบำรุงรักษาสิ่งนี้ไม่เพียง แ...บน 01/01/1970 66960

-

คู่มือการล้างวาล์ว: ฟังก์ชั่นอาการการทดสอบและการเปลี่ยนประสิทธิภาพของเครื่องยนต์ที่ดีที่สุด

วาล์วล้างเป็นส่วนสำคัญของระบบรถยนต์ที่ช่วยให้อากาศสะอาดโดยการจัดการไอระเหยเชื้อเพลิงก่อนที่พวกเขาจะสามารถหลบหนีไปสู่ชั้นบรรยากาศได้สิ่งนี้ไม่เพียง แต่ช่วยสิ่งแวดล้อมด้วยการลดมลพิษ แต่ยังทำให้รถทำงา...บน 01/01/1970 63098

-

คุณภาพ (q) ปัจจัย: สมการและแอปพลิเคชัน

ปัจจัยด้านคุณภาพหรือ 'Q' เป็นสิ่งสำคัญเมื่อตรวจสอบว่าตัวเหนี่ยวนำและ resonators ทำงานได้ดีเพียงใดในระบบอิเล็กทรอนิกส์ที่ใช้ความถี่วิทยุ (RF)'Q' วัดว่าวงจรช่วยลดการสูญเสียพลังงานและส่งผลกระทบต่อช่วง...บน 01/01/1970 63040

-

บรรลุประสิทธิภาพสูงสุดด้วยทฤษฎีการถ่ายโอนพลังงานสูงสุด

ทฤษฎีบทการถ่ายโอนพลังงานสูงสุดอธิบายว่าพลังงานจากแหล่งกำเนิดเช่นแบตเตอรี่หรือเครื่องกำเนิดไฟฟ้าจะไหลไปยังโหลดที่เชื่อมต่อได้อย่างไรมันแสดงเงื่อนไขที่แน่นอนที่โหลดได้รับพลังงานมากที่สุดบทความนี้ครอบ...บน 01/01/1970 54097

-

ข้อมูลจำเพาะและความเข้ากันได้ของแบตเตอรี่ A23

แบตเตอรี่ A23 เป็นแบตเตอรี่รูปทรงกระบอกขนาดเล็กที่มีแรงดันไฟฟ้าสูงเรียกอีกอย่างว่า 23A, 23AE หรือ MN21 มันทำงานที่ 12 โวลต์และสูงกว่าแบตเตอรี่ AA หรือ AAA มากการออกแบบพิเศษทำให้เหมาะสำหรับ...บน 01/01/1970 52184