คู่มือ EPM7256SQC208-10: คุณสมบัติ, pinout, การเขียนโปรแกรม, แอปพลิเคชันและแผ่นข้อมูล

คู่มือนี้เกี่ยวกับ EPM7256SQC208-10 ซึ่งเป็นชิปที่ตั้งโปรแกรมได้ซึ่งทำโดย Intel (เดิมโดย Altera)มันมาจากตระกูลMax® 7000s และเป็นที่รู้จักกันดีว่าเป็นโปรแกรมที่รวดเร็วเชื่อถือได้และง่ายต่อการตั้งโปรแกรมในขณะที่อยู่ในอุปกรณ์แล้วบทความนี้อธิบายสิ่งที่ชิปทำวิธีการทำงานอย่างไรที่ใช้และทำไมมันถึงเป็นตัวเลือกที่ดีถ้าคุณต้องการอุปกรณ์ตรรกะที่แข็งแกร่งและยืดหยุ่นสำหรับโครงการของคุณแคตตาล็อก

ภาพรวม EPM7256SQC208-10

ที่ EPM7256SQC208-10 เป็นส่วนหนึ่งของตระกูล Intel (เดิมชื่อ Altera) Max® 7000s ซึ่งเป็นช่วง CPLD ที่มีประสิทธิภาพสูงที่รู้จักกันดีสำหรับความสามารถในการโปรแกรมที่แข็งแกร่งและความสามารถในการเพิ่มประสิทธิภาพตรรกะรุ่นนี้มีประตูที่ใช้งานได้ประมาณ 5,000 ประตูและรวมถึง 256 macrocells ซึ่งตั้งอยู่ในแพ็คสี่เหลี่ยมจัตุรัสพลาสติกขนาด 208 พิน (PQFP)มันทำงานที่ความถี่สูงถึง 128.2 MHz และรองรับแรงดันไฟฟ้า 5.0 V โดยมีความล่าช้าในการแพร่กระจายสูงสุด 7.5 ns และเพดานอุณหภูมิการทำงาน +70 ° Cคุณสมบัติที่สำคัญคือความสามารถในการโปรแกรมในระบบผ่าน IEEE STD ในตัว1149.1 อินเตอร์เฟส JTAG เปิดใช้งานการกำหนดค่าแบบไดนามิกอุปกรณ์MAX® 7000S ถูกประดิษฐ์ขึ้นโดยใช้เทคโนโลยี CMOS ขั้นสูงนำเสนอคุณสมบัติเช่นความล่าช้าของตรรกะแบบพินต่อพินอย่างรวดเร็วถึง 5 ns และความถี่เคาน์เตอร์สูงถึง 175.4 MHzครอบครัวนำเสนอตัวเลือกแพ็คเกจที่หลากหลายและได้รับการออกแบบด้วย flip-flop macrocell ที่ตั้งโปรแกรมได้ซึ่งนำไปสู่การประหยัดพลังงานอย่างมากมากกว่าการลดลง 50% ในบางกรณีนอกจากนี้ยังมีบิตรักษาความปลอดภัยสำหรับการปกป้องการออกแบบที่เป็นกรรมสิทธิ์

หากองค์กรของคุณต้องการโซลูชันตรรกะที่ตั้งโปรแกรมได้อย่างดี EPM7256SQC208-10 เป็นตัวเลือกที่เชื่อถือได้ดังนั้นติดต่อเราวันนี้เพื่อรักษาความปลอดภัยคำสั่งซื้อจำนวนมากของคุณ

EPM7256SQC208-10 CAD รุ่น

สัญลักษณ์ EPM7256SQC208-10

EPM7256SQC208-10 รอยเท้า

EPM7256SQC208-10 รุ่น 3D

คุณสมบัติ EPM7256SQC208-10

- ความหนาแน่นของตรรกะสูง: EPM7256SQC208-10 ให้ประตูที่ใช้งานได้ประมาณ 5,000 ประตูและมี 256 macrocellsความสามารถในการตรรกะที่สูงนี้ทำให้เหมาะสำหรับการใช้วงจรผสมที่ซับซ้อนและการรวมตรรกะที่มีประสิทธิภาพในการออกแบบขนาดกะทัดรัด

- ประสิทธิภาพที่รวดเร็ว: ด้วยความถี่ในการทำงานสูงสุดที่ 128.2 MHz และความล่าช้าในการแพร่กระจายเพียง 7.5 ns CPLD นี้ช่วยให้มั่นใจได้ว่าการประมวลผลอย่างรวดเร็วและเวลาตอบสนองที่รวดเร็วเหมาะสำหรับแอปพลิเคชันความเร็วสูง

- ความสามารถในการโปรแกรมในระบบ (ISP): ติดตั้ง IEEE std1149.1 JTAG อินเตอร์เฟสอุปกรณ์ช่วยให้การเขียนโปรแกรมและการทดสอบในระบบโดยไม่จำเป็นต้องกำจัดทางกายภาพอำนวยความสะดวกในการพัฒนาซ้ำและการอัปเดต

- สถาปัตยกรรมขั้นสูง: การใช้สถาปัตยกรรม MAX รุ่นที่สองของ Altera และประดิษฐ์ด้วยเทคโนโลยี CMOS ขั้นสูง EPM7256SQC208-10 นำเสนอประสิทธิภาพและความทนทานที่เพิ่มขึ้นทำให้มั่นใจได้ถึงความน่าเชื่อถือในสภาพแวดล้อมการปฏิบัติงานที่หลากหลาย

- การจัดการพลังงาน: อุปกรณ์มีโหมดประหยัดพลังงานที่ตั้งโปรแกรมได้ซึ่งสามารถลดการใช้พลังงานได้มากกว่า 50% ต่อ macrocell สนับสนุนการออกแบบที่ประหยัดพลังงานและยืดอายุการใช้งานแบตเตอรี่ในแอพพลิเคชั่นแบบพกพา

- คุณสมบัติด้านความปลอดภัย: บิตรักษาความปลอดภัยที่ตั้งโปรแกรมได้ให้การป้องกันการเข้าถึงที่ไม่ได้รับอนุญาตและการคัดลอกการออกแบบที่เป็นกรรมสิทธิ์การปกป้องทรัพย์สินทางปัญญาอย่างมีประสิทธิภาพ

- สภาพการทำงานที่กว้าง: ทำงานที่ 5.0 V และสามารถทำงานได้ในอุณหภูมิสูงถึง +70 ° C CPLD นี้ปรับให้เข้ากับสภาพแวดล้อมที่หลากหลายทำให้เหมาะสำหรับการใช้งานทั้งในอุตสาหกรรมและเชิงพาณิชย์

- มาตรฐาน I/O ที่ยืดหยุ่น : รองรับการทำงานของอินเตอร์เฟส Multivolt ™ I/O ซึ่งเข้ากันได้กับระบบ 3.3 V และ 5.0 Vความยืดหยุ่นนี้ช่วยให้การรวมเข้ากับฮาร์ดแวร์ที่มีอยู่และใหม่ได้อย่างราบรื่นลดความซับซ้อนของระบบและค่าใช้จ่าย

- สนับสนุนการออกแบบ: EPM7256SQC208-10 ได้รับการสนับสนุนโดยเครื่องมือออกแบบและตัวเลือกฮาร์ดแวร์การเขียนโปรแกรมที่หลากหลายทำให้กระบวนการพัฒนาง่ายขึ้นและช่วยให้สามารถมุ่งเน้นไปที่นวัตกรรมมากกว่าปัญหาความเข้ากันได้

EPM7256SQC208-10 Pinout Diagram

แผนภาพนี้แสดงเค้าโครง PIN สำหรับชิป EPM7256SQC208-10 จาก Alteraชิปมี 208 พินจัดทั้งสี่ด้านในรูปสี่เหลี่ยมจัตุรัสพิน 1 เริ่มต้นที่มุมบนซ้ายและตัวเลขไปรอบ ๆ ชิปในทิศทางทวนเข็มนาฬิกาลงด้านซ้ายไปยังพิน 53 ด้านล่างถึงพิน 105 ขึ้นไปทางด้านขวาถึงพิน 157 และกลับไปทางขวาบนฉลากช่วยให้คุณรู้ว่าจะเริ่มต้นที่ไหนและวางชิปอย่างถูกต้องบนแผงวงจรชื่อในใจกลาง“ EPM7256E / EPM7256S” หมายถึงเลย์เอาต์นี้ใช้ได้กับชิปทั้งสองรุ่นแผนภาพนี้มีความสำคัญเมื่อเชื่อมต่อพลังงานสัญญาณหรือสายการเขียนโปรแกรมเข้ากับชิป

EPM7256SQC208-10 บล็อกไดอะแกรม

แผนภาพบล็อกของ EPM7256SQC208-10 แสดงให้เห็นว่าชิปถูกจัดระเบียบเพื่อจัดการงานตรรกะดิจิตอลอย่างไรมันมีบล็อกตรรกะหลักสี่บล็อกที่เรียกว่า Lab A, B, C และ D แต่ละบล็อกมี 16 macrocells ซึ่งเป็นชิ้นส่วนอาคารพื้นฐานที่ทำงานตรรกะดังนั้นโดยรวมมี 64 macrocells ภายในชิปรอบตรรกะเหล่านี้คือบล็อกควบคุม I/O ซึ่งเชื่อมต่อชิปกับโลกภายนอกผ่านหมุดอินพุตและเอาต์พุตบล็อกควบคุมแต่ละตัวจัดการหมุด 6 ถึง 16 พินปล่อยสัญญาณเข้าหรือออกจากชิปตามต้องการ

ตรงกลางคืออาร์เรย์เชื่อมต่อระหว่างกันที่ตั้งโปรแกรมได้ (PIA) ซึ่งทำหน้าที่เหมือนระบบทางหลวงทำให้สัญญาณเคลื่อนที่ระหว่างบล็อกลอจิกและหมุด I/Oสิ่งนี้ช่วยให้คุณสามารถกำหนดเส้นทางข้อมูลในแบบที่คุณต้องการสำหรับการออกแบบที่ด้านบนซ้ายแผนภาพแสดงอินพุตควบคุมบางอย่างเช่น Global Clock (GCLK), เอาต์พุตเปิดใช้งาน (OE) และ Clear (GCLR)สัญญาณเหล่านี้ช่วยจัดการเวลาและพฤติกรรมของวงจรลอจิกข้ามชิป

ข้อมูลจำเพาะ EPM7256SQC208-10

|

พิมพ์ |

พารามิเตอร์ |

|

ผู้ผลิต |

Altera/Intel |

|

ชุด |

Max® 7000S |

|

การบรรจุหีบห่อ |

ถาด |

|

สถานะชิ้นส่วน |

ล้าสมัย |

|

ประเภทที่ตั้งโปรแกรมได้ |

ในระบบที่ตั้งโปรแกรมได้ |

|

เวลาหน่วงเวลา tpd (1) สูงสุด |

10 ns |

|

แรงดันไฟฟ้า - ภายใน |

4.75V ~ 5.25V |

|

จำนวนองค์ประกอบตรรกะ/บล็อก |

16 |

|

จำนวน macrocells |

256 |

|

จำนวนประตู |

5,000 |

|

จำนวน I/O |

164 |

|

อุณหภูมิการทำงาน |

0 ° C ~ 70 ° C (TA) |

|

ประเภทการติดตั้ง |

ติดตั้งพื้นผิว |

|

แพ็คเกจ / เคส |

208-BFQFP |

|

แพ็คเกจอุปกรณ์ซัพพลายเออร์ |

208-PQFP (28x28) |

|

หมายเลขผลิตภัณฑ์พื้นฐาน |

EPM7256 |

แอปพลิเคชัน EPM7256SQC208-10

ระบบอัตโนมัติอุตสาหกรรม

EPM7256SQC208-10 ใช้อย่างกว้างขวางในระบบระบบอัตโนมัติอุตสาหกรรมความหนาแน่นของตรรกะสูงและประสิทธิภาพที่รวดเร็วช่วยให้งานควบคุมที่ซับซ้อนเชื่อมต่อกับเซ็นเซอร์และแอคทูเอเตอร์ได้อย่างราบรื่นCPLD นี้เหมาะสำหรับการเพิ่มความแม่นยำและประสิทธิภาพในสายการผลิตระบบควบคุมกระบวนการและแอปพลิเคชันหุ่นยนต์

โทรคมนาคม

ในการสื่อสารโทรคมนาคม CPLD นี้เก่งในการจัดการการไหลของข้อมูลและความสมบูรณ์ของสัญญาณในเครือข่ายรองรับฟังก์ชั่นเช่นการแปลงสัญญาณการกำหนดเส้นทางและการประมวลผลในสวิตช์และเราเตอร์เพื่อให้มั่นใจว่าโครงสร้างพื้นฐานการสื่อสารที่แข็งแกร่งและมีประสิทธิภาพ

ระบบยานยนต์

ในอุตสาหกรรมยานยนต์อุปกรณ์นี้มีส่วนช่วยในความน่าเชื่อถือและความซับซ้อนของระบบเช่นหน่วยการจัดการเครื่องยนต์ระบบสาระบันเทิงและเทคโนโลยีการช่วยเหลือผู้ขับขี่ประสิทธิภาพที่แข็งแกร่งภายใต้เงื่อนไขที่แตกต่างกันทำให้เหมาะสำหรับการใช้งานที่สำคัญต่อความปลอดภัย

อุปกรณ์การแพทย์

ความแม่นยำและความสามารถในการโปรแกรมของ EPM7256SQC208-10 ทำให้มันมีค่าในอุปกรณ์การแพทย์ที่การควบคุมที่แม่นยำและการทำงานที่เชื่อถือได้มีความสำคัญมันถูกใช้ในอุปกรณ์สำหรับการตรวจสอบ vitals ของผู้ป่วยจัดการเครื่องมือวินิจฉัยและการส่งมอบการรักษาอัตโนมัติ

การบินและอวกาศและการป้องกัน

ในการบินและอวกาศและการป้องกัน EPM7256SQC208-10 ใช้ในระบบที่ต้องการความน่าเชื่อถือและประสิทธิภาพในระดับสูงเช่นการสื่อสารผ่านดาวเทียมเครื่องช่วยนำทางและการควบคุมฮาร์ดแวร์ทางทหารความสามารถในการทำงานภายใต้เงื่อนไขที่รุนแรงเป็นประโยชน์

สถาบันการศึกษาและการวิจัย

CPLD นี้ยังได้รับความนิยมในการตั้งค่าการศึกษาและโครงการวิจัยซึ่งความสามารถในการ reprogrammability และความยืดหยุ่นช่วยให้การทดลองและการเรียนรู้ในการออกแบบดิจิทัลและอุปกรณ์อิเล็กทรอนิกส์ช่วยให้ต้นแบบและทดสอบการออกแบบตรรกะต่างๆได้อย่างมีประสิทธิภาพ

EPM7256SQC208-10 ชิ้นส่วนที่คล้ายกัน

ขั้นตอนการเขียนโปรแกรม EPM7256SQC208-10

1. เข้าสู่โหมด ISP

ขั้นตอนเริ่มต้นนี้มีความสำคัญเนื่องจากการเปลี่ยน CPLD จากโหมดการทำงานปกติเป็นโหมดการเขียนโปรแกรมในระบบ (ISP)สิ่งนี้ทำได้โดยการส่งคำสั่งเฉพาะผ่านอินเตอร์เฟส JTAGในระหว่างกระบวนการนี้พิน I/O ทั้งหมดของ CPLD นั้นมีการระบุไว้สามครั้ง (ปิดใช้งาน) เพื่อหลีกเลี่ยงการรบกวนหรือความขัดแย้งใด ๆ กับส่วนประกอบวงจรอื่น ๆการเปลี่ยนผ่านเข้าสู่โหมด ISP เตรียมอุปกรณ์สำหรับการเขียนโปรแกรมที่ปลอดภัยและใช้เวลาประมาณ 1 มิลลิวินาที

2. ตรวจสอบรหัส

เมื่ออยู่ในโหมด ISP ระบบจะทำการตรวจสอบ ID เพื่อให้แน่ใจว่าอุปกรณ์ที่ถูกต้องกำลังถูกตั้งโปรแกรมไว้สิ่งนี้เกี่ยวข้องกับการอ่านรหัสซิลิคอนที่ไม่ซ้ำกันของอุปกรณ์ผ่านอินเตอร์เฟส JTAGขั้นตอนนี้ดีสำหรับการตรวจสอบว่าคำสั่งการเขียนโปรแกรมและข้อมูลจะถูกส่งไปยังอุปกรณ์ที่ถูกต้องป้องกันการเขียนโปรแกรมที่ผิดพลาดและความเสียหายของอุปกรณ์ที่อาจเกิดขึ้น

3. ลบจำนวนมาก

ก่อนที่จะตั้งโปรแกรมข้อมูลใหม่ข้อมูลที่มีอยู่ภายใน CPLD จะต้องถูกลบขั้นตอนการลบจำนวนมากล้างเซลล์ที่ตั้งโปรแกรมได้อย่างมีประสิทธิภาพภายในอุปกรณ์สิ่งนี้ทำได้โดยการเปลี่ยนคำสั่งลบจากนั้นใช้ชีพจร 100 มิลลิวินาทีซึ่งลบชิปทั้งหมดขั้นตอนนี้มีความสำคัญเพื่อให้แน่ใจว่าไม่มีการกำหนดค่าก่อนหน้านี้รบกวนการเขียนโปรแกรมใหม่

4. โปรแกรม

ขั้นตอนนี้เกี่ยวข้องกับการเขียนโปรแกรมจริงของ CPLD ซึ่งข้อมูลการกำหนดค่าใหม่ถูกเขียนลงในอุปกรณ์ข้อมูลและที่อยู่ที่เกี่ยวข้องจะถูกเลื่อนเข้าไปในอุปกรณ์ผ่านอินเตอร์เฟส JTAGแต่ละที่อยู่และคู่ข้อมูลต้องใช้พัลส์การเขียนโปรแกรมเพื่อให้แน่ใจว่าข้อมูลถูกเขียนลงในเซลล์หน่วยความจำที่ไม่ระเหยของ CPLD อย่างถูกต้องขั้นตอนนี้ซ้ำสำหรับแต่ละจุดข้อมูลทั่วแผนที่หน่วยความจำของอุปกรณ์

5. ยืนยัน

โพสต์โปรแกรมจำเป็นต้องตรวจสอบว่าข้อมูลได้ถูกเขียนลงในอุปกรณ์อย่างถูกต้องขั้นตอนการตรวจสอบนี้เกี่ยวข้องกับการอ่านข้อมูลที่ตั้งโปรแกรมไว้จากแต่ละที่อยู่และเปรียบเทียบกับข้อมูลอินพุตดั้งเดิมขั้นตอนนี้ทำให้มั่นใจได้ว่าข้อมูลความสมบูรณ์ของข้อมูลและยืนยันว่ากระบวนการเขียนโปรแกรมประสบความสำเร็จโดยไม่มีข้อผิดพลาดใด ๆ

6. ออกจากโหมด ISP

ขั้นตอนสุดท้ายในกระบวนการเขียนโปรแกรมคือการออกจากโหมด ISP และส่งคืน CPLD ไปยังโหมดการทำงานปกติสิ่งนี้ทำได้โดยการส่งคำสั่งอื่นผ่านอินเตอร์เฟส JTAGเมื่อออกจากทางออกที่ประสบความสำเร็จหมุด I/O จะถูกเปิดใช้งานใหม่และอุปกรณ์จะดำเนินการต่อฟังก์ชั่นปกติขั้นตอนนี้มักจะใช้เวลาประมาณ 1 มิลลิวินาที

EPM7256SQC208-10 ข้อดี

การกำหนดค่าที่ไม่ระเหย

EPM7256SQC208-10 ใช้เทคโนโลยี EEPROM ทำให้สามารถจัดเก็บการกำหนดค่าได้อย่างถาวรลักษณะที่ไม่ระเหยนี้หมายความว่าอุปกรณ์ไม่จำเป็นต้องโหลดข้อมูลการกำหนดค่าใหม่จากหน่วยความจำภายนอกทุกครั้งที่เปิดใช้งานสิ่งนี้ส่งผลให้เวลาเริ่มต้นเร็วขึ้นและลดความซับซ้อนโดยรวมของการออกแบบฮาร์ดแวร์โดยไม่จำเป็นต้องใช้ส่วนประกอบการจัดเก็บข้อมูลเพิ่มเติม

ความสามารถในการโปรแกรมในระบบ (ISP)

หนึ่งในคุณสมบัติที่โดดเด่นของ EPM7256SQC208-10 คือการสนับสนุนความสามารถในการโปรแกรมในระบบสิ่งนี้จะช่วยให้อุปกรณ์ได้รับการตั้งโปรแกรมและ reprogrammed ในขณะที่ฝังตัวในแอปพลิเคชันสุดท้ายโดยไม่จำเป็นต้องถูกลบออกทางร่างกายความสามารถนี้ทำให้การอัปเดตและการดัดแปลงง่ายขึ้นให้ความยืดหยุ่นและความสะดวกในการใช้งานในระหว่างการพัฒนาและตลอดวงจรชีวิตของผลิตภัณฑ์

การนับ I/O สูงและความหนาแน่นของตรรกะ

อุปกรณ์นำเสนอทรัพยากรตรรกะจำนวนมากและหมุด I/O ที่มี 256 macrocells และหมุด I/O ผู้ใช้ 164 คนการนับ I/O ที่สูงและความหนาแน่นของตรรกะนี้ช่วยให้การรวมฟังก์ชั่นหลายฟังก์ชั่นเข้ากับชิปเดียวช่วยให้การออกแบบที่ซับซ้อนมากขึ้นในขณะที่อนุรักษ์พื้นที่บน PCBข้อได้เปรียบนี้เป็นประโยชน์ในการใช้งานที่พื้นที่บอร์ดอยู่ในระดับพรีเมี่ยมและอเนกประสงค์เป็นสิ่งสำคัญ

การหน่วงเวลา Pin-to-Pin ที่รวดเร็ว

ด้วยความล่าช้าสูงสุดถึงพินถึงพินเพียง 10 ns EPM7256SQC208-10 สามารถดำเนินการตรรกะความเร็วสูงได้เวลาตอบสนองที่รวดเร็วนี้ยอดเยี่ยมในแอพพลิเคชั่นที่ต้องการความสามารถในการประมวลผลอย่างรวดเร็วเช่นการสื่อสารความเร็วสูงหรือคอมพิวเตอร์เพื่อให้มั่นใจว่าระบบตรงตามเกณฑ์ประสิทธิภาพที่เข้มงวด

ความเข้ากันได้ของแรงดันไฟฟ้ากว้าง

EPM7256SQC208-10 ได้รับการออกแบบให้มีความยืดหยุ่นในแง่ของความเข้ากันได้ของแรงดันไฟฟ้ารองรับการทำงานภายในที่ระดับ 5 V และ I/O ที่ 3.3 V. ความสามารถในการใช้แรงดันไฟฟ้าคู่นี้ช่วยให้อุปกรณ์สามารถเชื่อมต่อได้อย่างง่ายดายทั้ง 3.3 V และ 5 V

ขนาดบรรจุภัณฑ์ EPM7256SQC208-10

- ประเภทแพ็คเกจ: 208-BFQFP (แพ็คเกจแบนสี่เหลี่ยมจัตุรัสพลาสติก)

- จำนวนพิน: 208 ผู้นำ

- ขนาดร่างกาย (L × W): 28 มม. × 28 มม.

- รูปแบบการติดตั้ง: เทคโนโลยี Mount Surface (SMT)

- สนามตะกั่ว: โดยทั่วไป 0.5 มม. ระหว่างพิน (มาตรฐานสำหรับ BFQFP)

- วัสดุบรรจุภัณฑ์: พลาสติก

- ความหนาของบรรจุภัณฑ์: ประมาณ 3.5 มม. (แตกต่างกันเล็กน้อยตามผู้ผลิต)

- ลักษณะความร้อน: ไม่มีแผ่นสัมผัส;การกระจายโดยรอบมาตรฐานผ่านบอร์ด

- บรรจุภัณฑ์ถาด: จัดหาในถาดสำหรับการจัดการระดับเสียงและระบบอัตโนมัติแบบเลือกและสถานที่

EPM7256SQC208-10 ผู้ผลิต

EPM7256SQC208-10 ได้รับการพัฒนาและผลิตโดยเดิม Altera Corporationผู้บุกเบิกชั้นนำในอุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซึ่งรู้จักกันดีในซีรี่ส์Max® 7000S ของ CPLDsในปี 2558 Altera ได้มาโดย Intel Corporationหนึ่งในผู้ผลิตเซมิคอนดักเตอร์ที่ใหญ่ที่สุดในโลกนับตั้งแต่การเข้าซื้อกิจการ Intel ยังคงให้การสนับสนุนและรวมเทคโนโลยี CPLD และ FPGA ของ Altera อย่างต่อเนื่องภายใต้กลุ่มโซลูชันที่ตั้งโปรแกรมได้EPM7256SQC208-10 แสดงถึงมรดกของ Intel ในการนำเสนอโซลูชั่นตรรกะที่มีประสิทธิภาพสูงและมีประสิทธิภาพสูงในระบบที่เหมาะสำหรับการใช้งานด้านอุตสาหกรรมการสื่อสารโทรคมนาคมและแอพพลิเคชั่นฝังตัวแม้ว่าตอนนี้จะถูกจัดเป็นล้าสมัย แต่ส่วนนี้สะท้อนให้เห็นถึงความมุ่งมั่นที่ยาวนานของ Intel ต่ออุปกรณ์ตรรกะที่น่าเชื่อถือและยืดหยุ่น

บทสรุป

EPM7256SQC208-10 เป็นชิปที่ชาญฉลาดและเชื่อถือได้ซึ่งช่วยให้ระบบดิจิตอลทำงานได้อย่างราบรื่นช่วยประหยัดพลังงานรองรับแรงดันไฟฟ้าที่แตกต่างกันและให้คุณตั้งโปรแกรมในขณะที่ติดตั้งแล้วซึ่งทำให้การอัปเดตง่ายขึ้นแม้ว่าตอนนี้จะเป็นชิปรุ่นเก่า แต่คนอื่น ๆ ก็ยังใช้มันเพราะมันทำงานได้ดีในทุกระบบหากคุณต้องการชิปที่เป็นของแข็งสำหรับการควบคุมตรรกะในการออกแบบของคุณอันนี้เป็นตัวเลือกที่ยอดเยี่ยมติดต่อเราวันนี้หากคุณต้องการสั่งซื้อเป็นกลุ่ม

PDF แผ่นข้อมูล

EPM7256SQC208-10 แผ่นข้อมูล:

ซอฟต์แวร์แผ่นดิสก์ 06/พฤศจิกายน/2020.pdf

เกี่ยวกับเรา

ALLELCO LIMITED

อ่านเพิ่มเติม

สอบถามรายละเอียดเพิ่มเติมอย่างรวดเร็ว

กรุณาส่งคำถามเราจะตอบกลับทันที

คำถามที่พบบ่อย [FAQ]

1. เครื่องมือการเขียนโปรแกรมใดที่เข้ากันได้กับ EPM7256SQC208-10

คุณสามารถใช้ซอฟต์แวร์ Quartus II ของ Intel (เดิมคือ Altera Quartus) พร้อมกับโปรแกรมเมอร์ที่เข้ากันได้กับ JTAG เช่น USB-BLASTER เพื่อกำหนดค่าและตั้งโปรแกรม EPM7256SQC208-10 โดยตรงในระบบ

2. ฉันสามารถ reprogram EPM7256SQC208-10 หลายครั้งได้หรือไม่?

ใช่ EPM7256SQC208-10 รองรับรอบการเขียนโปรแกรมซ้ำหลายรอบโดยใช้การโปรแกรมการโปรแกรมในระบบ EEPROM ทำให้เหมาะอย่างยิ่งสำหรับการพัฒนาการออกแบบซ้ำหรือการอัปเดตหลังการปรับใช้

3. EPM7256SQC208-10 สามารถจัดการกับสภาพการทำงานที่รุนแรงได้หรือไม่?

มันทำงานได้อย่างน่าเชื่อถือภายในช่วงอุณหภูมิเชิงพาณิชย์ 0 ° C ถึง +70 ° C ซึ่งเพียงพอสำหรับการใช้งานอุตสาหกรรมและการฝังตัวส่วนใหญ่แม้ว่าจะไม่ใช่สภาพแวดล้อมที่รุนแรงหรือเกรดยานยนต์

4. ฉันยังสามารถตั้งโปรแกรม EPM7256SQC208-10 โดยไม่ต้องลบออกจากแผงวงจรได้หรือไม่?

ใช่.ชิปรองรับการโปรแกรมในระบบ (ISP) ผ่าน JTAG ช่วยให้คุณสามารถ reprogram ได้ในขณะที่มันบัดกรีลงบนกระดานของคุณประหยัดเวลาและความพยายามในระหว่างการพัฒนาหรือการบำรุงรักษา

5. อะไรทำให้ EPM7256SQC208-10 ดีกว่าไมโครคอนโทรลเลอร์มาตรฐานสำหรับงานตรรกะ?

ซึ่งแตกต่างจากไมโครคอนโทรลเลอร์ EPM7256SQC208-10 เป็น CPLD ซึ่งเก่งในการดำเนินการลอจิกแบบขนานพร้อมเวลาที่แม่นยำเหมาะอย่างยิ่งเมื่อคุณต้องการการควบคุมดิจิตอลที่รวดเร็วและกำหนดได้มากกว่าสัญญาณหลายสัญญาณ

ทฤษฎีบทของ Demorgan อธิบาย: การทำให้การแสดงออกของตรรกะง่ายขึ้นเพื่อการออกแบบวงจรที่ดีขึ้น

บน 25/04/2025

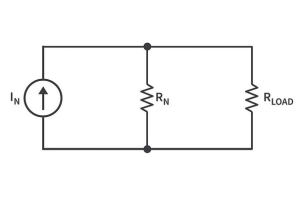

พื้นฐานทฤษฎีบทของนอร์ตันและตัวอย่างวงจร

บน 24/04/2025

โพสต์ยอดนิยม

-

คอมพิวเตอร์ชุดคำสั่งที่ซับซ้อน: พวกเขาเปลี่ยนการคำนวณอย่างไร?

บน 18/04/8000 147772

-

USB-C Pinout และคุณสมบัติ

บน 18/04/2000 112010

-

การใช้ Xilinx Unified Simulation Primitives: คู่มือที่ครอบคลุมสำหรับการออกแบบและการจำลอง FPGA

บน 18/04/1600 111351

-

การทำความเข้าใจแรงดันไฟฟ้าของแหล่งจ่ายไฟในอิเล็กทรอนิกส์ VCC, VDD, VEE, VSS และ GND

บน 18/04/0400 83769

-

คู่มือเชื่อมต่อ RJ45: Pinout, การเดินสาย, ประเภทสายเคเบิลและการใช้งาน

บน 01/01/1970 79565

-

คู่มือที่ดีที่สุดสำหรับรหัสสีลวดในระบบไฟฟ้าที่ทันสมัย

วิธีที่ระบบไฟฟ้าของเราใช้สีไม่ได้มีไว้สำหรับรูปลักษณ์ตอนนี้สีลวดแต่ละอันบ่งบอกถึงฟังก์ชั่นเฉพาะทำให้ง่ายต่อการระบุและจัดการส่วนประกอบไฟฟ้าอย่างถูกต้องระหว่างการติดตั้งและบำรุงรักษาสิ่งนี้ไม่เพียง แ...บน 01/01/1970 66960

-

คู่มือการล้างวาล์ว: ฟังก์ชั่นอาการการทดสอบและการเปลี่ยนประสิทธิภาพของเครื่องยนต์ที่ดีที่สุด

วาล์วล้างเป็นส่วนสำคัญของระบบรถยนต์ที่ช่วยให้อากาศสะอาดโดยการจัดการไอระเหยเชื้อเพลิงก่อนที่พวกเขาจะสามารถหลบหนีไปสู่ชั้นบรรยากาศได้สิ่งนี้ไม่เพียง แต่ช่วยสิ่งแวดล้อมด้วยการลดมลพิษ แต่ยังทำให้รถทำงา...บน 01/01/1970 63100

-

คุณภาพ (q) ปัจจัย: สมการและแอปพลิเคชัน

ปัจจัยด้านคุณภาพหรือ 'Q' เป็นสิ่งสำคัญเมื่อตรวจสอบว่าตัวเหนี่ยวนำและ resonators ทำงานได้ดีเพียงใดในระบบอิเล็กทรอนิกส์ที่ใช้ความถี่วิทยุ (RF)'Q' วัดว่าวงจรช่วยลดการสูญเสียพลังงานและส่งผลกระทบต่อช่วง...บน 01/01/1970 63040

-

บรรลุประสิทธิภาพสูงสุดด้วยทฤษฎีการถ่ายโอนพลังงานสูงสุด

ทฤษฎีบทการถ่ายโอนพลังงานสูงสุดอธิบายว่าพลังงานจากแหล่งกำเนิดเช่นแบตเตอรี่หรือเครื่องกำเนิดไฟฟ้าจะไหลไปยังโหลดที่เชื่อมต่อได้อย่างไรมันแสดงเงื่อนไขที่แน่นอนที่โหลดได้รับพลังงานมากที่สุดบทความนี้ครอบ...บน 01/01/1970 54097

-

ข้อมูลจำเพาะและความเข้ากันได้ของแบตเตอรี่ A23

แบตเตอรี่ A23 เป็นแบตเตอรี่รูปทรงกระบอกขนาดเล็กที่มีแรงดันไฟฟ้าสูงเรียกอีกอย่างว่า 23A, 23AE หรือ MN21 มันทำงานที่ 12 โวลต์และสูงกว่าแบตเตอรี่ AA หรือ AAA มากการออกแบบพิเศษทำให้เหมาะสำหรับ...บน 01/01/1970 52184