HDL: ปลดล็อคนวัตกรรมในการออกแบบวงจรดิจิตอล

คู่มือนี้สำรวจภาษาคำอธิบายฮาร์ดแวร์ (HDLs) เครื่องมือสำคัญสำหรับการเปลี่ยนการออกแบบนามธรรมให้กลายเป็นวงจรจริงที่ผลิตได้เราครอบคลุมวิวัฒนาการการใช้งานในการออกแบบ ASIC และ FPGA และผลกระทบต่ออุปกรณ์อิเล็กทรอนิกส์ที่ทันสมัยด้วยตัวอย่างและข้อมูลเชิงลึกของผู้เชี่ยวชาญคู่มือนี้มีจุดมุ่งหมายเพื่อให้เข้าใจ HDLS และเสริมสร้างทั้งทฤษฎีและทักษะการปฏิบัติของคุณให้ลึกซึ้งยิ่งขึ้นค้นพบวิธีที่ HDLS เชื่อมช่องว่างระหว่างความคิดและอุปกรณ์ทางกายภาพขับเคลื่อนนวัตกรรมในเทคโนโลยีแคตตาล็อก

บทบาทของ HDL ในการออกแบบดิจิทัล

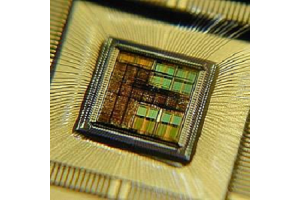

Hardware Description Language (HDL) มีบทบาทในการออกแบบระบบดิจิตอลโดยให้วิธีที่มีโครงสร้างในการจำลองวงจรที่ซับซ้อนช่วยให้สามารถแบ่งระบบขนาดใหญ่ออกเป็นโมดูลขนาดเล็กที่จัดการได้ซึ่งได้รับการทดสอบและตรวจสอบโดยใช้เครื่องมือการออกแบบระบบอัตโนมัติแบบอิเล็กทรอนิกส์ (EDA)เมื่อตรวจสอบแล้วโมดูลเหล่านี้จะถูกสังเคราะห์เป็น Netlists ระดับประตูและเปลี่ยนเป็นวงจรทางกายภาพผ่านการจัดวาง ASIC หรือ FPGA และการกำหนดเส้นทางใช้กันอย่างแพร่หลายในอุตสาหกรรมเช่น Silicon Valley, HDL ขับเคลื่อนนวัตกรรมโดยช่วยปรับสมดุลการออกแบบข้อ จำกัด ด้วยโซลูชั่นสร้างสรรค์ทำให้เป็นองค์ประกอบสำคัญในการพัฒนาเทคโนโลยีดิจิตอล

การพัฒนาประวัติศาสตร์ของ HDL

การพัฒนาของฮาร์ดแวร์คำอธิบายภาษา (HDLS) ครอบคลุมหลายทศวรรษพัฒนาจากเครื่องมือเฉพาะที่แยกส่วนเป็นโซลูชั่นมาตรฐานทั่วทั้งอุตสาหกรรมเช่น VHDL และ Verilog ในช่วงปลายทศวรรษ 1980HDLS แบบครบวงจรที่ได้มาตรฐานเหล่านี้และการทำงานร่วมกันที่ดีขึ้นในฐานะที่เป็นเทคโนโลยีขั้นสูง HDLs ได้ขยายตัวเพื่อรองรับระบบที่ซับซ้อนมากขึ้นเชื่อมโยงฮาร์ดแวร์และการออกแบบซอฟต์แวร์ด้วยภาษาใหม่เช่น SystemC และ SuperlogHDLs ได้แสดงคุณค่าในการปรับปรุงการสื่อสารลดข้อผิดพลาดและปรับปรุงกระบวนการออกแบบวิวัฒนาการอย่างต่อเนื่องของ HDLs สะท้อนให้เห็นถึงความต้องการนวัตกรรมอย่างต่อเนื่องเพื่อตอบสนองความต้องการที่เปลี่ยนแปลงของการออกแบบดิจิทัลสำหรับการพัฒนาเทคโนโลยีที่ทันสมัย

วัตถุประสงค์

ในขณะที่วงจรรวมมีความซับซ้อนมากขึ้นโดยได้รับแรงหนุนจากกฎหมายของมัวร์ตั้งแต่ปี 1970 วิธีการออกแบบได้เปลี่ยนจากการมุ่งเน้นไปที่ส่วนประกอบแต่ละตัวไปสู่การจัดการการไหลของข้อมูลระดับระบบและเวลาการเปลี่ยนแปลงนี้นำไปสู่การยอมรับการลงทะเบียนระดับการถ่ายโอน (RTL) สิ่งที่เป็นนามธรรมซึ่งอนุญาตให้มีสมาธิกับฟังก์ชั่นลอจิกและเวลาโดยไม่จำเป็นต้องระบุรายละเอียดการผลิตก่อนRTL Abstraction ซึ่งได้รับการสนับสนุนโดย Hardware Description Languages (HDLs), ปรับปรุงกระบวนการออกแบบโดยการปรับสมดุลประสิทธิภาพพลังงานและความสามารถในการปรับขนาดช่วยลดวัฏจักรการออกแบบเพิ่มความร่วมมือและช่วยคาดการณ์ปัญหาที่อาจเกิดขึ้นป้องกันการแก้ไขที่มีราคาแพงโดยการมุ่งเน้นไปที่ระดับนามธรรมที่สูงขึ้นคุณจะปลดล็อกประสิทธิภาพการปรับตัวและนวัตกรรมในภูมิทัศน์เทคโนโลยีที่พัฒนาขึ้นอย่างรวดเร็ว

ลักษณะโครงสร้าง

ฮาร์ดแวร์คำอธิบายภาษา (HDLs) ทำหน้าที่เป็นกรอบข้อความที่กำหนดโครงสร้างพฤติกรรมและเวลาของระบบวงจรพวกเขาทำหน้าที่เหมือนภาษาการเขียนโปรแกรมแบบขนาน แต่มุ่งเน้นไปที่การจัดการเวลาและการเชื่อมต่อฮาร์ดแวร์โดยเฉพาะHDLS ดำเนินการในระดับที่เป็นนามธรรมต่าง ๆ โครงสร้างพฤติกรรมและการถ่ายโอนการลงทะเบียนเพื่อเข้าใกล้การออกแบบวงจรจากมุมมองที่แตกต่างกันในระดับโครงสร้างส่วนประกอบและการเชื่อมต่อรายละเอียด HDLS คล้ายกับแผนผังระดับพฤติกรรมมุ่งเน้นไปที่สิ่งที่วงจรควรทำในขณะที่ระดับการถ่ายโอนการลงทะเบียน (RTL) อธิบายการไหลของข้อมูลและการดำเนินงานระหว่างการลงทะเบียนการทำงานที่สมดุลและเฉพาะฮาร์ดแวร์HDLS ยังสนับสนุนการสังเคราะห์ตรรกะการแปลงการออกแบบระดับสูงเป็นวงจรระดับประตูและการจำลองซึ่งทดสอบการทำงานก่อนการปรับใช้ฮาร์ดแวร์ซึ่งแตกต่างจากภาษาการเขียนโปรแกรมแบบดั้งเดิม HDLs เป็นเครื่องมือในการสร้างแบบจำลองที่จับพฤติกรรมฮาร์ดแวร์ทำให้พวกเขามีความสำคัญสำหรับการออกแบบวงจรที่ถูกต้องและเป็นนวัตกรรม

การตรวจสอบการไหลของข้อมูลใน HDL

ซึ่งแตกต่างจากภาษาการเขียนโปรแกรมแบบดั้งเดิมที่จัดลำดับความสำคัญของการควบคุมการไหล HDLs มุ่งเน้นไปที่การสร้างแบบจำลองการไหลของข้อมูลและเวลาในวงจรสำหรับการพัฒนาและการจำลองฮาร์ดแวร์ความสามารถพิเศษนี้ในการจับพฤติกรรมชั่วคราวของฮาร์ดแวร์ทำให้ HDLs นอกเหนือจากภาษาเช่น C ++HDL ที่ทันสมัยเช่น SystemVerilog กำลังผสมผสานกระบวนทัศน์การเขียนโปรแกรมที่ผสมผสานกันมากขึ้นโดยรวมแนวคิดเชิงวัตถุเพื่อปรับปรุงความเป็นโมดูลและการบำรุงรักษาในการออกแบบระบบที่ซับซ้อนHDLS ยังมีบทบาทในการสังเคราะห์ตรรกะเปลี่ยนคำอธิบายระดับสูงเป็นการใช้งานระดับประตูเพื่อให้มั่นใจว่าการออกแบบนามธรรมสอดคล้องกับข้อ จำกัด ทางกายภาพนอกจากนี้ยังใช้องค์ประกอบ HDL ที่ไม่สามารถสังเคราะห์ได้สำหรับการจำลองและการตรวจสอบเพื่อทดสอบพฤติกรรมวงจรอย่างเข้มงวดก่อนการผลิตในขณะที่ HDLs ยังคงพัฒนาอย่างต่อเนื่องพวกเขามีแนวโน้มที่จะนำคุณสมบัติที่คล้ายกับซอฟต์แวร์มาใช้เพื่อจัดการกับความซับซ้อนของฮาร์ดแวร์ที่เพิ่มขึ้นลดช่องว่างระหว่างความแม่นยำของฮาร์ดแวร์และสิ่งที่เป็นมิตรที่เป็นมิตร

เพิ่มการออกแบบวงจรแบบบูรณาการด้วย HDL

ฮาร์ดแวร์คำอธิบายภาษา (HDLS) ปรับปรุงกระบวนการที่ซับซ้อนในการออกแบบวงจรรวมโดยการเปลี่ยนแนวคิดนามธรรมให้กลายเป็นแผนการดำเนินการที่ใช้งานได้จริงหลายคนมักใช้ผังงานและไดอะแกรมสถานะเพื่อแมปตรรกะวงจรก่อนที่จะแปลงเป็นรหัส HDL ที่แม่นยำเช่นการสร้างพิมพ์เขียวสำหรับการก่อสร้างในขณะที่ยึดติดกับข้อกำหนดของวงจรคนอื่น ๆ นำสไตล์ที่เป็นเอกลักษณ์มาใช้ในการเข้ารหัสโดยการรวมอัลกอริทึมและสคริปต์เพื่อทำให้งานซ้ำ ๆ ง่ายขึ้นเครื่องมือตรวจสอบข้อผิดพลาดจากนั้นระบุปัญหาก่อนกำหนดเพื่อให้มั่นใจถึงความน่าเชื่อถือก่อนการสังเคราะห์หลังจากการสังเคราะห์ NetLists จะเตรียมพร้อมสำหรับการผลิตไม่ว่าจะเป็น FPGAs หรือ ASICS โดยมุ่งเน้นไปที่ข้อกำหนดของอุปกรณ์เพื่อหลีกเลี่ยงความท้าทายในการผลิตHDLs สร้างความสมดุลระหว่างความคิดสร้างสรรค์และความแม่นยำทำให้การออกแบบวงจรที่เป็นนวัตกรรม แต่เชื่อถือได้ซึ่งมีความก้าวหน้าอย่างมีประสิทธิภาพจากแนวคิดไปสู่การรับรู้ทางกายภาพ

เกี่ยวกับเรา

ALLELCO LIMITED

อ่านเพิ่มเติม

สอบถามรายละเอียดเพิ่มเติมอย่างรวดเร็ว

กรุณาส่งคำถามเราจะตอบกลับทันที

แพลตฟอร์มซอฟต์แวร์ Vitis Unified: เร่งระบบฝังตัวและการคำนวณแบบปรับตัวด้วย Xilinx

บน 07/01/2025

วิวัฒนาการและความก้าวหน้าเชิงกลยุทธ์ในเทคโนโลยี VLSI

บน 06/01/2025

โพสต์ยอดนิยม

-

คอมพิวเตอร์ชุดคำสั่งที่ซับซ้อน: พวกเขาเปลี่ยนการคำนวณอย่างไร?

บน 18/04/8000 147753

-

USB-C Pinout และคุณสมบัติ

บน 18/04/2000 111928

-

การใช้ Xilinx Unified Simulation Primitives: คู่มือที่ครอบคลุมสำหรับการออกแบบและการจำลอง FPGA

บน 18/04/1600 111349

-

การทำความเข้าใจแรงดันไฟฟ้าของแหล่งจ่ายไฟในอิเล็กทรอนิกส์ VCC, VDD, VEE, VSS และ GND

บน 18/04/0400 83714

-

คู่มือเชื่อมต่อ RJ45: Pinout, การเดินสาย, ประเภทสายเคเบิลและการใช้งาน

บน 01/01/1970 79504

-

คู่มือที่ดีที่สุดสำหรับรหัสสีลวดในระบบไฟฟ้าที่ทันสมัย

วิธีที่ระบบไฟฟ้าของเราใช้สีไม่ได้มีไว้สำหรับรูปลักษณ์ตอนนี้สีลวดแต่ละอันบ่งบอกถึงฟังก์ชั่นเฉพาะทำให้ง่ายต่อการระบุและจัดการส่วนประกอบไฟฟ้าอย่างถูกต้องระหว่างการติดตั้งและบำรุงรักษาสิ่งนี้ไม่เพียง แ...บน 01/01/1970 66872

-

คุณภาพ (q) ปัจจัย: สมการและแอปพลิเคชัน

ปัจจัยด้านคุณภาพหรือ 'Q' เป็นสิ่งสำคัญเมื่อตรวจสอบว่าตัวเหนี่ยวนำและ resonators ทำงานได้ดีเพียงใดในระบบอิเล็กทรอนิกส์ที่ใช้ความถี่วิทยุ (RF)'Q' วัดว่าวงจรช่วยลดการสูญเสียพลังงานและส่งผลกระทบต่อช่วง...บน 01/01/1970 63005

-

คู่มือการล้างวาล์ว: ฟังก์ชั่นอาการการทดสอบและการเปลี่ยนประสิทธิภาพของเครื่องยนต์ที่ดีที่สุด

วาล์วล้างเป็นส่วนสำคัญของระบบรถยนต์ที่ช่วยให้อากาศสะอาดโดยการจัดการไอระเหยเชื้อเพลิงก่อนที่พวกเขาจะสามารถหลบหนีไปสู่ชั้นบรรยากาศได้สิ่งนี้ไม่เพียง แต่ช่วยสิ่งแวดล้อมด้วยการลดมลพิษ แต่ยังทำให้รถทำงา...บน 01/01/1970 62959

-

บรรลุประสิทธิภาพสูงสุดด้วยทฤษฎีการถ่ายโอนพลังงานสูงสุด

ทฤษฎีบทการถ่ายโอนพลังงานสูงสุดอธิบายว่าพลังงานจากแหล่งกำเนิดเช่นแบตเตอรี่หรือเครื่องกำเนิดไฟฟ้าจะไหลไปยังโหลดที่เชื่อมต่อได้อย่างไรมันแสดงเงื่อนไขที่แน่นอนที่โหลดได้รับพลังงานมากที่สุดบทความนี้ครอบ...บน 01/01/1970 54079

-

ข้อมูลจำเพาะและความเข้ากันได้ของแบตเตอรี่ A23

แบตเตอรี่ A23 เป็นแบตเตอรี่รูปทรงกระบอกขนาดเล็กที่มีแรงดันไฟฟ้าสูงเรียกอีกอย่างว่า 23A, 23AE หรือ MN21 มันทำงานที่ 12 โวลต์และสูงกว่าแบตเตอรี่ AA หรือ AAA มากการออกแบบพิเศษทำให้เหมาะสำหรับ...บน 01/01/1970 52093