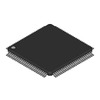

ความเข้าใจ ISPPAC-CLK5320S-01TN64C เครื่องกำเนิดนาฬิกาที่ตั้งโปรแกรมได้

ISPPAC-CLK5320S-01TN64C เป็นเครื่องกำเนิดนาฬิกาที่ตั้งโปรแกรมได้ซึ่งออกแบบมาเพื่อช่วยจัดการและแจกจ่ายสัญญาณนาฬิกาด้วยความแม่นยำมันมีเอาต์พุตหลายเอาต์พุตความถี่ที่ปรับได้และเบ้ต่ำทำให้เป็นตัวเลือกที่ยอดเยี่ยมสำหรับแอปพลิเคชันที่ต้องใช้เวลาที่แม่นยำด้วยเทคโนโลยีลูปเฟสล็อค (PLL) ในตัวทำให้มั่นใจได้ว่าการซิงโครไนซ์ที่เชื่อถือได้ในส่วนประกอบที่แตกต่างกันอุปกรณ์รองรับมาตรฐานนาฬิกาที่หลากหลายและช่วยให้สามารถปรับแต่งได้ง่ายทำให้เหมาะสำหรับระบบที่หลากหลายไม่ว่าคุณจะต้องการบัฟเฟอร์การล่าช้าการแบ่งความถี่หรือการกำหนดเส้นทางสัญญาณที่ยืดหยุ่นเครื่องกำเนิดนาฬิกานี้ให้ประสิทธิภาพที่คุณต้องการนอกจากนี้ยังมีการสนับสนุน JTAG สำหรับการเขียนโปรแกรมในระบบทำให้การตั้งค่าและการกำหนดค่าง่ายขึ้นบทความนี้สำรวจคุณสมบัติฟังก์ชั่นแอปพลิเคชันและรายละเอียดทางเทคนิคแคตตาล็อก

ภาพรวมของ ISPPAC-CLK5320S-01TN64C

ที่ ISPPAC-CLK5320S-01TN64C เป็นบัฟเฟอร์พัดลมแบบ Zero-Delay ที่ได้รับการตั้งโปรแกรมอเนกประสงค์ที่ออกแบบมาสำหรับแอพพลิเคชั่นการแจกแจงนาฬิกามันมีเอาต์พุตที่มีความเบ้ต่ำถึง 12 พิเศษโดยมีเอาต์พุตแต่ละคู่ที่ปรับแต่งได้เพื่อรองรับมาตรฐาน I/O ที่หลากหลายเช่น LVTTL, LVCMOS, SSTL และ HSTLผู้ใช้สามารถปรับความถี่เอาต์พุตการเลิกจ้างอัตราการฆ่าและเวลาเอียงอย่างอิสระสำหรับแต่ละเอาต์พุต

ด้วย PLL ที่มีประสิทธิภาพสูงอุปกรณ์นี้ช่วยให้มั่นใจได้ว่าการขยายตัวของการแพร่กระจายน้อยที่สุดมันมีตัวนับ 5 บิตที่ตั้งโปรแกรมได้สามตัวเพื่อสร้างความถี่หลายความถี่ซึ่งสามารถกำหนดเส้นทางไปยังพินเอาท์พุทใด ๆอุปกรณ์มีโหมดการทำงานสี่โหมดรวมถึงตัวเลือกบัฟเฟอร์การหน่วงเวลาที่ไม่เป็นศูนย์และไม่ใช่ศูนย์

ไม่ว่าคุณจะต้องการหน่วยเดียวหรือจำนวนมาก ISPCLOCK5300S-01TN64C ให้โซลูชันการจัดการนาฬิกาที่มีความยืดหยุ่นและยืดหยุ่นติดต่อเราสำหรับตัวเลือกการจัดซื้อจำนวนมากและใช้ประโยชน์จากราคาที่แข่งขันได้ของเรา!

รายละเอียด Pinout ของ ISPPAC-CLK5320S-01TN64C

คุณสมบัติที่สำคัญของ ISPPAC-CLK5320S-01TN64C

การกำหนดค่าการทำงานสี่แบบ

ISPPAC-CLK5320S-01TN64C มีโหมดการทำงานที่ยืดหยุ่นสี่โหมดช่วยให้คุณเลือกการตั้งค่าที่ดีที่สุดสำหรับความต้องการการกระจายนาฬิกาของคุณโหมดบัฟเฟอร์การหน่วงเวลาเป็นศูนย์จะซิงโครไนซ์นาฬิกาอินพุตและเอาต์พุตด้วยการหน่วงเวลาน้อยที่สุดในขณะที่การหน่วงเวลาเป็นศูนย์และโหมดบัฟเฟอร์การหน่วงเวลาที่ไม่ใช่ศูนย์รวมทั้งสองฟังก์ชั่นเพื่อความยืดหยุ่นที่เพิ่มเข้ามาโหมดบัฟเฟอร์การหน่วงเวลาที่ไม่เป็นศูนย์แบบคู่ให้เส้นทางการหน่วงเวลาอิสระสองเส้นทางและบัฟเฟอร์การหน่วงเวลาที่ไม่ใช่ศูนย์พร้อมโหมดตัวแบ่งเอาต์พุตช่วยให้เอาต์พุตนาฬิกาที่แบ่งออกได้ด้วยการปรับกำหนดเวลาที่กำหนดเอง

ช่วงความถี่อินพุตและเอาต์พุตกว้าง

ด้วยการรองรับความถี่ตั้งแต่ 8MHz ถึง 267MHz อุปกรณ์นี้มีตัวเลือกการตอกบัตรที่หลากหลายทำให้เหมาะสำหรับแอปพลิเคชันเวลาที่แตกต่างกันไม่ว่าระบบของคุณจะต้องการสัญญาณต่ำหรือความถี่สูงความยืดหยุ่นนี้ช่วยให้มั่นใจได้ว่าการทำงานของอุปกรณ์ต่าง ๆ อย่างราบรื่น

เบ้และกระวนกระวายใจต่ำสำหรับเวลาที่แม่นยำ

อุปกรณ์นี้ให้เวลาสัญญาณที่แม่นยำโดยมีความเบ้เอาท์พุทไปยังเอาท์พุทน้อยกว่า 100PS และต่ำกว่า 70PS ยอดเขาถึงจุดสูงสุดค่าต่ำเหล่านี้ช่วยรักษาความสมบูรณ์ของสัญญาณและลดข้อผิดพลาดในการกำหนดเวลาในแอพพลิเคชั่นความเร็วสูงเพื่อให้มั่นใจว่าการทำงานที่ราบรื่นในวงจรที่ซับซ้อน

บัฟเฟอร์ Fan-Out ที่ตั้งโปรแกรมได้สูงสุด 20 ตัว

ISPPAC-CLK5320S-01TN64C ให้บริการบัฟเฟอร์ Fan-Out ที่ตั้งโปรแกรมได้สูงสุด 20 ตัวทำให้คุณสามารถควบคุมการกำหนดค่าเอาต์พุตได้อย่างเต็มที่รองรับมาตรฐานเอาต์พุตแบบปลายเดี่ยวหลายแบบรวมถึง LVTTL, LVCMOS, HSTL, EHSTL และ SSTLคุณสามารถปรับความต้านทานเอาต์พุตระหว่าง40Ωถึง70Ωโดยเพิ่มขึ้น5Ωและปรับเปลี่ยนอัตราการฆ่าเพื่อการเปลี่ยนสัญญาณที่ดีขึ้นนอกจากนี้อุปกรณ์ยังมีธนาคารเอาต์พุตสูงถึง 10 ธนาคารแต่ละแห่งมีแหล่งจ่ายไฟของตัวเอง (1.5V, 1.8V, 2.5V หรือ 3.3V) ช่วยให้ระดับแรงดันไฟฟ้าแยกต่างหากสำหรับเอาต์พุตที่แตกต่างกัน

PLL ที่มีประสิทธิภาพสูง

PLL ในตัวทำให้มั่นใจได้ว่าสัญญาณนาฬิกาที่มีเสถียรภาพและเชื่อถือได้ด้วยการตรวจจับล็อคที่ตั้งโปรแกรมได้เพื่อการตรวจสอบความแม่นยำมันมีสามตัวแบ่งเอาต์พุตที่ตั้งโปรแกรมได้ซึ่งทำงานในพลังของ 2 (1, 2, 4, 8, 16, 32) ทำให้การปรับความถี่ง่ายขึ้นตัวกรองลูปบนชิปช่วยลดเสียงรบกวนในขณะที่ความเข้ากันได้ของนาฬิกาสเปกตรัมการแพร่กระจายช่วยลดสัญญาณรบกวนทางแม่เหล็กไฟฟ้าอุปกรณ์รองรับทั้งข้อเสนอแนะทั้งภายในและภายนอกโดยมีตัวเลือกการซิงโครไนซ์นาฬิกาที่ยืดหยุ่น

การปรับเฟสที่แม่นยำ

คุณสามารถปรับแต่งแต่ละเอาต์พุตด้วยการปรับเฟสได้ถึง± 5ns เพื่อจัดตำแหน่งสัญญาณอย่างแม่นยำอุปกรณ์ให้การตั้งค่าเฟสที่ตั้งโปรแกรมได้แปดแบบด้วยขนาดขั้นต่ำขั้นต่ำ 156PS เพื่อให้มั่นใจว่าการควบคุมเวลาที่แม่นยำรองรับโหมดการปรับหยาบและละเอียดช่วยให้คุณสามารถตอบสนองความต้องการของระบบที่แตกต่างกัน

หลายโดเมนความถี่สัญญาณนาฬิกา

ISPPAC-CLK5320S-01TN64C รองรับโดเมนความถี่สัญญาณนาฬิกาที่แยกกันได้ถึงสามโดเมนทำให้สัญญาณกำหนดเวลาหลายครั้งสามารถจัดการได้อย่างมีประสิทธิภาพภายในอุปกรณ์เดียวคุณสมบัตินี้เหมาะสำหรับระบบที่ต้องการแหล่งนาฬิกาอิสระสำหรับส่วนประกอบที่แตกต่างกัน

อินพุตและข้อเสนอแนะของนาฬิกาที่ยืดหยุ่น

อุปกรณ์นี้มีช่วงของอินพุตที่ตั้งโปรแกรมได้และมาตรฐานข้อเสนอแนะรวมถึง LVTTL, LVCMOS, SSTL, HSTL, LVDS, LVPECL, HSTL ที่แตกต่างและ SSTL ที่แตกต่างกันการเลือกนาฬิกา A/B นาฬิกาช่วยให้สามารถสลับระหว่างแหล่งอินพุตได้ในขณะที่เส้นทางการตอบกลับที่ตั้งโปรแกรมได้รองรับ LVTTL, LVCMOS, SSTL และ HSTLนอกจากนี้การยกเลิกการตั้งโปรแกรมในตัวทำให้การจัดการสัญญาณง่ายขึ้นเพิ่มประสิทธิภาพโดยรวม

การปฏิบัติตามซ็อกเก็ตร้อน

ISPPAC-CLK5320S-01TN64C เป็นซ็อกเก็ตร้อนซึ่งหมายถึงอินพุตและเอาต์พุตทั้งหมดยังคงทำงานได้อย่างสมบูรณ์แม้ในระหว่างการแลกเปลี่ยนร้อนสิ่งนี้ทำให้มั่นใจได้ว่าการดำเนินการอย่างต่อเนื่องโดยไม่เสี่ยงต่อการสูญเสียข้อมูลหรือการหยุดชะงัก

การเขียนโปรแกรม JTAG และในระบบ

อุปกรณ์รองรับการสแกนขอบเขต JTAG และการเขียนโปรแกรมในระบบทำให้การกำหนดค่าและการทดสอบง่ายโดยไม่จำเป็นต้องลบออกจากวงจรสิ่งนี้ทำให้การดีบักและเร่งเวลาการพัฒนาง่ายขึ้น

ภูมิคุ้มกัน

ออกแบบมาเพื่อทนต่อเสียงรบกวนจากแหล่งจ่ายไฟอุปกรณ์นี้ช่วยให้มั่นใจได้ว่าการทำงานที่มั่นคงและเชื่อถือได้แม้ในสภาพแวดล้อมที่มีเสียงดังทางไฟฟ้าสิ่งนี้ทำให้เป็นตัวเลือกที่เหมาะสำหรับแอปพลิเคชันประสิทธิภาพสูงที่ต้องใช้การจัดการนาฬิกาที่แม่นยำ

ตัวเลือกอุณหภูมิและบรรจุภัณฑ์

ISPPAC-CLK5320S-01TN64C มีให้บริการทั้งในเชิงพาณิชย์ (0 ° C ถึง 70 ° C) และอุตสาหกรรม (-40 ° C ถึง 85 ° C) ช่วงอุณหภูมิเพื่อให้มั่นใจถึงประสิทธิภาพที่เชื่อถือได้ในสภาพแวดล้อมที่แตกต่างกันมันมาในแพ็คเกจ TQFP ขนาด 48 พินและ 64 พินทำให้ง่ายต่อการรวมเข้ากับระบบต่างๆ

ข้อกำหนดทางเทคนิค

ข้อกำหนดทางเทคนิคของสารกึ่งตัวนำ lattice, ISPPAC-CLK5320S-01TN64C

|

คุณลักษณะ |

ค่า |

|

ผู้ผลิต |

เซมิคอนดักเตอร์ขัดแตะ |

|

ชุด |

ispClock ™ |

|

พิมพ์ |

เครื่องกำเนิดนาฬิกา, การแจกจ่าย Fanout, Zero Delay Buffer |

|

จำนวนวงจร |

1 |

|

แรงดันไฟฟ้า - อุปทาน |

3V ~ 3.6V |

|

อุณหภูมิปฏิบัติการ |

0 ° C ~ 70 ° C |

|

ความถี่ - สูงสุด |

267MHz |

|

อัตราส่วน - อินพุต: เอาต์พุต |

2:20 |

|

PLL |

ใช่ด้วยบายพาส |

|

ตัวแบ่ง/ตัวคูณ |

ใช่/ไม่ใช่ |

|

ความแตกต่าง - อินพุต: เอาต์พุต |

ใช่/ไม่ใช่ |

|

ป้อนข้อมูล |

HSTL, LVCMOS, LVDS, LVPECL, LVTTL, SSTL |

|

เอาท์พุท |

EHSTL, HSTL, LVCMOS, LVTTL, SSTL |

|

แพ็คเกจ / เคส |

64-LQFP |

|

แพ็คเกจซัพพลายเออร์ |

64-TQFP (10x10) |

|

ประเภทการติดตั้ง |

ติดตั้งพื้นผิว |

|

บรรจุุภัณฑ์ |

ถาด |

|

หมายเลขผลิตภัณฑ์พื้นฐาน |

isppac-clk53 |

ไดอะแกรมบล็อกการทำงานของ ISPPAC-CLK5320S-01TN64C

แผนภาพแสดงให้เห็นว่า ISPPAC-CLK5320S-01TN64C ทำงานอย่างไรเป็นเครื่องกำเนิดนาฬิกาที่ตั้งโปรแกรมได้ต้องใช้สัญญาณนาฬิกาอ้างอิงหลายสัญญาณ (RefA, REFB) และสัญญาณตอบรับ (FBK) เพื่อให้ทุกอย่างอยู่ในการซิงค์อินพุตการเลือก (refsel) เลือกการอ้างอิงที่จะใช้เครื่องตรวจจับเฟสจะเปรียบเทียบการอ้างอิงที่เลือกกับสัญญาณตอบรับและตัวกรองลูปจะทำให้การเปลี่ยนแปลงใด ๆ ทำให้เกิดการเปลี่ยนแปลงใด ๆ ก่อนที่จะส่งสัญญาณไปยังออสซิลเลเตอร์ที่ควบคุมด้วยแรงดันไฟฟ้า (VCO)VCO สร้างนาฬิกาความถี่สูงซึ่งจะถูกแบ่งออกเป็นเอาต์พุตนาฬิกาที่แตกต่างกันเอาต์พุตเหล่านี้ผ่านเมทริกซ์การกำหนดเส้นทางซึ่งสามารถปรับได้สำหรับการกำหนดเวลา (การควบคุมเบ้) ก่อนที่จะถูกส่งผ่านไดรเวอร์เอาต์พุตระบบยังรวมถึงการควบคุมการเปิดใช้งานเอาต์พุตตัวเลือกบายพาส PLL และคุณสมบัติการตรวจจับล็อคเพื่อแสดงเมื่อทุกอย่างมีความเสถียรนอกจากนี้ยังมีอินเทอร์เฟซ JTAG สำหรับการเขียนโปรแกรมและการทดสอบการตั้งค่านี้ช่วยให้มั่นใจได้ว่าการกระจายนาฬิกาที่แม่นยำในส่วนต่าง ๆ ของระบบทำให้เป็นประโยชน์สำหรับโปรเซสเซอร์อุปกรณ์สื่อสารและวงจรดิจิตอลอื่น ๆ

การใช้งานและแอปพลิเคชันของ ISPPAC-CLK5320S-01TN64C

แผงวงจรการกระจายนาฬิกาทั่วไป

ISPPAC-CLK5320S-01TN64C ใช้กันอย่างแพร่หลายในการกระจายสัญญาณนาฬิกาทั่วไปข้ามแผงวงจรช่วยให้มั่นใจได้ว่าส่วนประกอบที่เชื่อมต่อทั้งหมดจะได้รับสัญญาณเวลาที่ซิงโครไนซ์ปรับปรุงการสื่อสารระหว่างส่วนต่าง ๆ ของระบบด้วยความเบ้และกระวนกระวายใจต่ำช่วยรักษาความแม่นยำของสัญญาณลดข้อผิดพลาดในการถ่ายโอนข้อมูล

การสร้างความถี่ตาม PLL

อุปกรณ์นี้มี PLL ที่มีประสิทธิภาพสูงช่วยให้คุณสามารถสร้างความถี่นาฬิกาที่เสถียรและตั้งโปรแกรมได้ไม่ว่าคุณจะต้องการคูณแบ่งหรือซิงโครไนซ์ความถี่ ISPPAC-CLK5320S-01TN64C ให้การจัดการนาฬิกาที่ยืดหยุ่นสำหรับช่วงของแอปพลิเคชันรวมถึงการประมวลผลข้อมูลระบบการสื่อสารและอุปกรณ์ฝังตัว

บัฟเฟอร์นาฬิกาที่มีพัดลมสูง

เมื่อสัญญาณนาฬิกาเดียวจำเป็นต้องขับเคลื่อนส่วนประกอบหลายส่วน ISPPAC-CLK5320S-01TN64C ทำหน้าที่เป็นบัฟเฟอร์พัดลมสูงที่เชื่อถือได้ด้วยเอาต์พุตที่ตั้งโปรแกรมได้สูงสุด 20 รายการสามารถกระจายสัญญาณนาฬิกาได้อย่างมีประสิทธิภาพในขณะที่ยังคงความเบ้ต่ำระหว่างเอาต์พุตสิ่งนี้มีประโยชน์ในระบบขนาดใหญ่ที่ระบบย่อยหลายระบบต้องการนาฬิกาที่ซิงโครไนซ์

บัฟเฟอร์นาฬิกา Zero-delay

ฟังก์ชั่นบัฟเฟอร์การล่าช้าเป็นศูนย์ของ ISPPAC-CLK5320S-01TN64C ทำให้มั่นใจได้ว่านาฬิกาเอาท์พุทยังคงอยู่ในแนวเดียวกันกับนาฬิกาอ้างอิงป้องกันไม่ให้เวลาไม่ตรงกันสิ่งนี้มีประโยชน์อย่างยิ่งในแอปพลิเคชันที่จำเป็นต้องมีการซิงโครไนซ์ที่แม่นยำเช่นอินเตอร์เฟสหน่วยความจำอุปกรณ์เครือข่ายและระบบประมวลผลข้อมูลความเร็วสูง

มิติโครงร่างของ ISPPAC-CLK5320S-01TN64C

แผนภาพให้ขนาดทางกายภาพและรายละเอียดการจัดวางของแพ็คเกจ ISPPAC-CLK5320S-01TN64Cมันมีมุมมองที่แตกต่างกัน-ด้านล่าง, ด้านล่าง, ด้านข้างและหน้าตัด-เพื่อให้ความคิดที่ชัดเจนเกี่ยวกับรูปร่างและขนาดของมันแพ็คเกจมี 64 พินจัดเรียงรอบขอบมุมมองด้านบนแสดงการจัดเรียง PIN โดยมีเครื่องหมายขนาดเล็กระบุพิน 1 สำหรับการวางแนวที่ถูกต้องมุมมองด้านล่างให้มุมมองที่คล้ายกัน แต่จากด้านล่าง

มุมมองด้านข้างเน้นความสูงของแพ็คเกจรูปร่างของโอกาสในการขายและวิธีที่พวกเขาขยายออกจากร่างกายการซูมเข้าอย่างละเอียด (รายละเอียด 'A') แสดงให้เห็นว่าโอกาสในการโค้งงอและสัมผัสกับแผงวงจรระนาบที่นั่งเป็นส่วนที่ติดต่อกับบอร์ดเมื่อติดตั้ง

ตารางแสดงรายการการวัดต่าง ๆ รวมถึงความสูงของแพ็คเกจความกว้างตะกั่วและระยะห่างระหว่างพินมิติทั้งหมดอยู่ในมิลลิเมตรหมายเหตุอธิบายความคลาดเคลื่อนวิธีการวัดแพ็คเกจและรายละเอียดเพิ่มเติมเช่นการยื่นออกมาของเชื้อราและการตกแต่งด้วยตะกั่วรูปร่างที่แน่นอนของมุมไม่ได้รับการแก้ไขซึ่งหมายความว่าอาจมีการเปลี่ยนแปลงเล็กน้อยการวาดภาพนี้ช่วยให้มั่นใจได้ว่าการติดตั้งที่เหมาะสมและการวางส่วนประกอบบนแผงวงจร

ทางเลือก isppac-clk5320s-01tn64c

|

หมายเลขชิ้นส่วน |

ผู้ผลิต |

คุณสมบัติที่สำคัญ |

ใช้เคส/หมายเหตุ |

|

เซมิคอนดักเตอร์ขัดแตะ |

คล้ายกับ ISPPAC-CLK5320S แต่มี 2:16 อัตราส่วนอินพุตต่อเอาท์พุทรองรับช่วงแรงดันไฟฟ้าความถี่และ รูปแบบเอาต์พุตหลายรูปแบบมาในแพ็คเกจ 64-TQFP |

เหมาะสำหรับการกระจายนาฬิกาในดิจิตอลขนาดกลาง ระบบที่ 16 เอาต์พุตเพียงพอ |

|

|

เซมิคอนดักเตอร์ขัดแตะ |

เวอร์ชันเอาต์พุตที่ต่ำกว่าที่มีอัตราส่วนอินพุตต่อเอาต์พุต 2:12 รองรับคุณสมบัตินาฬิกาเดียวกัน แต่ทำงานในช่วงอุณหภูมิที่กว้างขึ้น (-40 ° C ถึง 85 ° C)มาในแพ็คเกจ 48-TQFP ที่เล็กกว่า |

ดีที่สุดสำหรับการใช้งานอุตสาหกรรมที่ต้องการความแข็งแกร่ง การทนต่ออุณหภูมิและการกระจายนาฬิกาปานกลาง |

|

|

เซมิคอนดักเตอร์ขัดแตะ |

เสนอการแจกแจงนาฬิกา 8 เอาต์พุตที่มีความคล้ายคลึงกัน ชุดคุณสมบัติรวมถึง PLL รูปแบบอินพุต/เอาต์พุตหลายรูปแบบและสูงสุด ความถี่ 267MHzนอกจากนี้ยังทำงานในช่วง -40 ° C ถึง 85 ° C |

ออกแบบมาสำหรับการจัดการนาฬิกาขนาดกะทัดรัดและมีความน่าเชื่อถือสูง ในสภาพแวดล้อมที่รุนแรงหรือแอพพลิเคชั่นที่ จำกัด พื้นที่ |

เกี่ยวกับเซมิคอนดักเตอร์ขัดแตะ

Lattice Semiconductor พัฒนาโซลูชันที่มีประสิทธิภาพต่ำและมีประสิทธิภาพสูงสำหรับการจัดการนาฬิกาการเชื่อมต่อและการประมวลผลในฐานะผู้ผลิต ISPPAC-CLK5320S-01TN64C LATTICE ให้เทคโนโลยีการกระจายนาฬิกาที่เชื่อถือได้และยืดหยุ่นซึ่งออกแบบมาสำหรับเวลาและการซิงโครไนซ์ที่แม่นยำด้วยการมุ่งเน้นไปที่นวัตกรรมและประสิทธิภาพ Lattice ยังคงรองรับอุปกรณ์อิเล็กทรอนิกส์ที่ทันสมัยด้วยโซลูชั่นที่เชื่อถือได้และมีคุณภาพสูง

บทสรุป

ISPPAC-CLK5320S-01TN64C เป็นโซลูชันการจัดการนาฬิกาที่ยืดหยุ่นและเชื่อถือได้ซึ่งออกแบบมาเพื่อให้ระบบของคุณทำงานได้อย่างราบรื่นด้วยคุณสมบัติที่ตั้งโปรแกรมได้เบ้ต่ำและตัวเลือกเอาต์พุตหลายตัวเลือกทำให้มั่นใจได้ถึงเวลาที่แม่นยำสำหรับแอปพลิเคชันต่างๆไม่ว่าคุณจะต้องการบัฟเฟอร์การสร้างความถี่หรือการกระจายแบบพัดลมสูงอุปกรณ์นี้ให้ประสิทธิภาพและความยืดหยุ่นที่คุณต้องการหากคุณกำลังมองหาวิธีที่เชื่อถือได้ในการจัดการสัญญาณนาฬิกานี่เป็นตัวเลือกที่ยอดเยี่ยม

PDF แผ่นข้อมูล

ข้อมูล ISPPAC-CLK5320S-01TN64C:

เกี่ยวกับเรา

ALLELCO LIMITED

อ่านเพิ่มเติม

สอบถามรายละเอียดเพิ่มเติมอย่างรวดเร็ว

กรุณาส่งคำถามเราจะตอบกลับทันที

คำถามที่พบบ่อย [FAQ]

1. ISPPAC-CLK5320S-01TN64C ใช้สำหรับอะไร?

มันเป็นเครื่องกำเนิดนาฬิกาที่ตั้งโปรแกรมได้และบัฟเฟอร์ Fan-Out ที่ออกแบบมาเพื่อจัดการและแจกจ่ายสัญญาณนาฬิกาช่วยให้ส่วนต่าง ๆ ของระบบซิงโครไนซ์โดยการทำให้มั่นใจว่าเวลาที่แม่นยำ

2. ฉันสามารถปรับความถี่เอาต์พุตได้อย่างอิสระได้หรือไม่?

ใช่อุปกรณ์อนุญาตให้คุณตั้งค่าความถี่เอาต์พุตที่แตกต่างกันโดยใช้ตัวแบ่งที่ตั้งโปรแกรมได้แต่ละเอาต์พุตสามารถปรับให้ตรงกับความต้องการเวลาที่เฉพาะเจาะจง

3. สัญญาณนาฬิกาประเภทใดรองรับ?

รองรับมาตรฐานอินพุตและเอาต์พุตหลายอย่างรวมถึง LVTTL, LVCMOS, SSTL, HSTL, LVDS และ LVPECLสิ่งนี้ทำให้เข้ากันได้กับระบบและอุปกรณ์ที่แตกต่างกัน

4. โหมดบัฟเฟอร์การล่าช้าเป็นศูนย์ทำงานอย่างไร?

ในโหมดการล่าช้าศูนย์นาฬิกาอินพุตและเอาต์พุตจะอยู่ในแนวเดียวกันกับความล่าช้าน้อยที่สุดสิ่งนี้จะช่วยรักษาการซิงโครไนซ์ระหว่างส่วนประกอบต่าง ๆ ในวงจร

5. สนับสนุนการเขียนโปรแกรมในระบบหรือไม่?

ใช่มันมีอินเทอร์เฟซ JTAG สำหรับการเขียนโปรแกรมและการทดสอบในระบบสิ่งนี้ช่วยให้คุณสามารถกำหนดค่าได้โดยไม่ต้องลบออกจากวงจร

PCM vs. Dolby Digital: สุดยอดคู่มือสำหรับเทคโนโลยีเสียงที่มีความเที่ยงตรงสูงและเสียงรอบทิศทาง

บน 24/02/2025

คู่มือการซื้อสำหรับ EPM7256AETI144-7N ทุกสิ่งที่คุณจำเป็นต้องรู้

บน 21/02/2025

โพสต์ยอดนิยม

-

คอมพิวเตอร์ชุดคำสั่งที่ซับซ้อน: พวกเขาเปลี่ยนการคำนวณอย่างไร?

บน 17/04/8000 147713

-

USB-C Pinout และคุณสมบัติ

บน 17/04/2000 111731

-

การใช้ Xilinx Unified Simulation Primitives: คู่มือที่ครอบคลุมสำหรับการออกแบบและการจำลอง FPGA

บน 17/04/1600 111322

-

การทำความเข้าใจแรงดันไฟฟ้าของแหล่งจ่ายไฟในอิเล็กทรอนิกส์ VCC, VDD, VEE, VSS และ GND

บน 17/04/0400 83611

-

คู่มือเชื่อมต่อ RJ45: Pinout, การเดินสาย, ประเภทสายเคเบิลและการใช้งาน

บน 01/01/1970 79264

-

คู่มือที่ดีที่สุดสำหรับรหัสสีลวดในระบบไฟฟ้าที่ทันสมัย

วิธีที่ระบบไฟฟ้าของเราใช้สีไม่ได้มีไว้สำหรับรูปลักษณ์ตอนนี้สีลวดแต่ละอันบ่งบอกถึงฟังก์ชั่นเฉพาะทำให้ง่ายต่อการระบุและจัดการส่วนประกอบไฟฟ้าอย่างถูกต้องระหว่างการติดตั้งและบำรุงรักษาสิ่งนี้ไม่เพียง แ...บน 01/01/1970 66780

-

คุณภาพ (q) ปัจจัย: สมการและแอปพลิเคชัน

ปัจจัยด้านคุณภาพหรือ 'Q' เป็นสิ่งสำคัญเมื่อตรวจสอบว่าตัวเหนี่ยวนำและ resonators ทำงานได้ดีเพียงใดในระบบอิเล็กทรอนิกส์ที่ใช้ความถี่วิทยุ (RF)'Q' วัดว่าวงจรช่วยลดการสูญเสียพลังงานและส่งผลกระทบต่อช่วง...บน 01/01/1970 62947

-

คู่มือการล้างวาล์ว: ฟังก์ชั่นอาการการทดสอบและการเปลี่ยนประสิทธิภาพของเครื่องยนต์ที่ดีที่สุด

วาล์วล้างเป็นส่วนสำคัญของระบบรถยนต์ที่ช่วยให้อากาศสะอาดโดยการจัดการไอระเหยเชื้อเพลิงก่อนที่พวกเขาจะสามารถหลบหนีไปสู่ชั้นบรรยากาศได้สิ่งนี้ไม่เพียง แต่ช่วยสิ่งแวดล้อมด้วยการลดมลพิษ แต่ยังทำให้รถทำงา...บน 01/01/1970 62827

-

บรรลุประสิทธิภาพสูงสุดด้วยทฤษฎีการถ่ายโอนพลังงานสูงสุด

ทฤษฎีบทการถ่ายโอนพลังงานสูงสุดอธิบายว่าพลังงานจากแหล่งกำเนิดเช่นแบตเตอรี่หรือเครื่องกำเนิดไฟฟ้าจะไหลไปยังโหลดที่เชื่อมต่อได้อย่างไรมันแสดงเงื่อนไขที่แน่นอนที่โหลดได้รับพลังงานมากที่สุดบทความนี้ครอบ...บน 01/01/1970 54028

-

ข้อมูลจำเพาะและความเข้ากันได้ของแบตเตอรี่ A23

แบตเตอรี่ A23 เป็นแบตเตอรี่รูปทรงกระบอกขนาดเล็กที่มีแรงดันไฟฟ้าสูงเรียกอีกอย่างว่า 23A, 23AE หรือ MN21 มันทำงานที่ 12 โวลต์และสูงกว่าแบตเตอรี่ AA หรือ AAA มากการออกแบบพิเศษทำให้เหมาะสำหรับ...บน 01/01/1970 51990