EP20K100EFC324-1X FPGA: คุณสมบัติข้อมูลจำเพาะแอปพลิเคชันและคู่มือการเขียนโปรแกรม

EP20K100EFC324-1X เป็นชิปที่ตั้งโปรแกรมได้ (FPGA) จากซีรี่ส์ Altera Apex-20KE®ของ Intelมันถูกออกแบบมาเพื่อจัดการวงจรดิจิตอลที่ซับซ้อนและรองรับการประมวลผลข้อมูลความเร็วสูงคู่มือนี้อธิบายคุณสมบัติข้อกำหนดวิธีการเขียนโปรแกรมและข้อดีของมันทำให้เป็นทรัพยากรที่เป็นประโยชน์สำหรับทุกคนแคตตาล็อก

ภาพรวม EP20K100EFC324-1X

ที่ EP20K100EFC324-1X เป็นส่วนหนึ่งของซีรี่ส์ Altera Apex-20KE®ของ Intel ซึ่งเป็นเกตอาเรย์ที่ตั้งโปรแกรมได้ (FPGA) ที่เหมาะสำหรับแอปพลิเคชั่นตรรกะที่ตั้งโปรแกรมได้สูงซึ่งจำเป็นต้องมีการรวมระบบที่มีความซับซ้อนในการรวมระบบ (SOPC)อุปกรณ์นี้โดดเด่นด้วยการรวมองค์ประกอบตรรกะหรือเซลล์ตรรกะ 4,160 และ 416 บล็อกอาร์เรย์ลอจิก (LABS) ซึ่งอำนวยความสะดวกในการกำหนดค่าที่สำคัญสำหรับการออกแบบวงจรดิจิตอลต่างๆนอกจากนี้ยังมีหน่วยความจำฝังตัวจำนวนมากที่รองรับข้อกำหนดการจัดเก็บข้อมูลที่ต้องการภายใน FPGAเพิ่มความสามารถในการใช้งานที่หลากหลายของแอปพลิเคชัน EP20K100EFC324-1X รองรับหมุด 246 I/O และมีจำนวนประตูที่มีค่าประมาณ 263,000 ประตูเทียบเท่าประตูที่มีประสิทธิภาพระหว่าง 1.71V ถึง 1.89Vมันถูกบรรจุในชุดกริดบอลบอลขนาด 324 บอล (FBGA) ซึ่งช่วยในการรวมทางกายภาพที่แข็งแกร่งเข้ากับชุดประกอบอิเล็กทรอนิกส์

EP20K100EFC324-1X เป็นตัวเลือกที่สมบูรณ์แบบเมื่อคุณพร้อมที่จะสั่งซื้อจำนวนมากกับเราสำหรับโครงการหรือสายผลิตภัณฑ์ของคุณ

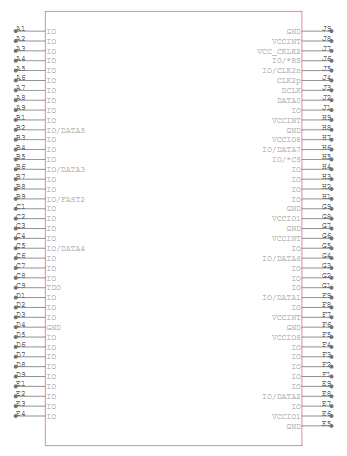

รุ่น EP20K100EFC324-1X CAD

สัญลักษณ์ EP20K100EFC324-1X

EP20K100EFC324-1X

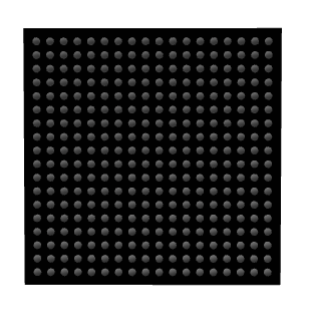

รุ่น EP20K100EFC324-1X 3D

คุณสมบัติ EP20K100EFC324-1X

- ความหนาแน่นของตรรกะสูง: FPGA มีการติดตั้งองค์ประกอบตรรกะ 4,160 (LES) และ 416 บล็อกอาร์เรย์ลอจิก (ห้องปฏิบัติการ)ความหนาแน่นสูงของเซลล์ตรรกะนี้ช่วยให้การออกแบบและการดำเนินการของวงจรดิจิตอลที่ซับซ้อนและระบบภายในชิปเดียวทำให้เหมาะสำหรับแอปพลิเคชันที่ต้องการความสามารถในการประมวลผลตรรกะที่แข็งแกร่ง

- หน่วยความจำฝัง: นำเสนอบิต RAM 53,248 ตัว FPGA นี้ให้ทรัพยากรหน่วยความจำฝังตัวที่สำคัญคุณลักษณะนี้เหมาะสำหรับแอปพลิเคชันที่ต้องการการจัดเก็บข้อมูลและการดึงข้อมูลที่รวดเร็วทำให้สามารถจัดการงานที่ต้องใช้ข้อมูลได้อย่างมีประสิทธิภาพ

- ความสามารถ I/O ที่กว้างขวาง: ด้วยหมุดอินพุต/เอาต์พุต 246 ตัว EP20K100EFC324-1X ทำให้มั่นใจได้ว่าการเชื่อมต่อที่ครอบคลุมและตัวเลือกการเชื่อมต่อความสามารถ I/O ที่หลากหลายนี้ช่วยให้สามารถเชื่อมต่อกับอุปกรณ์และระบบภายนอกได้อย่างง่ายดายเพิ่มยูทิลิตี้ในชุดประกอบอิเล็กทรอนิกส์ที่ซับซ้อน

- การสนับสนุนหลายโวลต์: อุปกรณ์รองรับช่วงแรงดันไฟฟ้าหลักที่ 1.71V ถึง 1.89V และคุณสมบัติการเชื่อมต่อ Multivolt ™ I/Oสิ่งนี้ช่วยให้ FPGA เข้ากันได้กับส่วนประกอบอิเล็กทรอนิกส์อื่น ๆ ที่ทำงานในระดับตรรกะต่างๆรวมถึง 1.8V, 2.5V, 3.3V และ 5.0V ให้ความยืดหยุ่นในการออกแบบระบบ

ไดอะแกรมบล็อก EP20K100EFC324-1X

ที่ ไดอะแกรมบล็อก EP20K100EFC324-1X แสดงถึงโครงสร้างภายในของอุปกรณ์ Gate Gate Array (Field Programmable Array) อุปกรณ์แสดงหน่วยการทำงานต่าง ๆแผนภาพประกอบด้วยบล็อกตรรกะที่เชื่อมต่อกันองค์ประกอบหน่วยความจำการจัดการนาฬิกาและองค์ประกอบ I/Oที่สำคัญของการออกแบบคือ บล็อกอาร์เรย์ลอจิก (ห้องปฏิบัติการ) ซึ่งมี ตารางค้นหา (LUTS) และตรรกะตามผลิตภัณฑ์องค์ประกอบเหล่านี้ช่วยให้การใช้ตรรกะที่ยืดหยุ่นทำให้ FPGA เหมาะสำหรับตรรกะการควบคุมความเร็วสูงเครื่องจักรสถานะและฟังก์ชั่น DSPที่ Fasttrack Interconnect ให้เส้นทางการสื่อสารความเร็วสูงระหว่างองค์ประกอบตรรกะเพื่อให้มั่นใจว่าการกำหนดเส้นทางสัญญาณที่มีประสิทธิภาพทั่วทั้งอุปกรณ์ที่ วงจรการจัดการนาฬิกา รวมถึงคุณสมบัติของ clocklock ทำให้มั่นใจได้ว่าการทำงานที่เชื่อถือได้และซิงโครไนซ์โดยการทำให้เสถียรและกระจายสัญญาณนาฬิกาทั่ว FPGAที่ องค์ประกอบอินพุต/เอาต์พุต (IOES) วางอยู่รอบ ๆ ผ้า FPGA ทำหน้าที่เป็นส่วนต่อประสานสำหรับการสื่อสารภายนอกไอโอเหล่านี้สนับสนุนโปรโตคอลมาตรฐานอุตสาหกรรมหลายแห่งเช่น PCI- GTL+- SSTL-3, และ LVDSช่วยให้ FPGA สามารถเชื่อมต่อกับระบบภายนอกที่หลากหลายIOE เหล่านี้สร้างความมั่นใจในความเข้ากันได้กับระดับแรงดันไฟฟ้าที่แตกต่างกันและมาตรฐานการส่งสัญญาณเพิ่มความสามารถรอบด้านของ FPGA ในแอปพลิเคชันที่ฝังตัว บล็อกหน่วยความจำฝัง จัดหาโซลูชันการจัดเก็บที่ยืดหยุ่นภายใน FPGAองค์ประกอบหน่วยความจำเหล่านี้สามารถทำงานเป็น หน่วยความจำที่อยู่เนื้อหาได้ (ลูกเบี้ยว), หน่วยความจำการเข้าถึงแบบสุ่ม (ราม), หน่วยความจำแบบอ่านอย่างเดียว (รอม), ครั้งแรกในครั้งแรก (FIFO) บัฟเฟอร์และโครงสร้างหน่วยความจำอื่น ๆความสามารถในการรวมหน่วยความจำโดยตรงภายในผ้า FPGA ช่วยปรับปรุงประสิทธิภาพการประมวลผลข้อมูลลดการพึ่งพาหน่วยความจำภายนอกและเวลาแฝง

ข้อมูลจำเพาะ EP20K100EFC324-1X

|

พิมพ์ |

พารามิเตอร์ |

|

ผู้ผลิต |

Intel |

|

ชุด |

APEX-20KE® |

|

การบรรจุหีบห่อ |

ถาด |

|

สถานะชิ้นส่วน |

ล้าสมัย |

|

จำนวนห้องปฏิบัติการ/CLBS |

416 |

|

จำนวนองค์ประกอบตรรกะ/เซลล์ |

4160 |

|

บิตแรมทั้งหมด |

53248 |

|

จำนวน I/O |

246 |

|

จำนวนประตู |

263000 |

|

แรงดันไฟฟ้า - อุปทาน |

1.71V ~ 1.89V |

|

ประเภทการติดตั้ง |

ติดตั้งพื้นผิว |

|

อุณหภูมิการทำงาน |

0 ° C ~ 85 ° C (TJ) |

|

แพ็คเกจ / เคส |

324-BGA |

|

แพ็คเกจอุปกรณ์ซัพพลายเออร์ |

324-FBGA (19x19) |

|

หมายเลขผลิตภัณฑ์พื้นฐาน |

EP20K100 |

แอปพลิเคชัน EP20K100EFC324-1X

เครือข่ายและการสื่อสาร

FPGA นี้เหมาะสำหรับอุปกรณ์เครือข่ายเช่นเราเตอร์และสวิตช์ซึ่งจะจัดการการกำหนดเส้นทางข้อมูลการประมวลผลสัญญาณและการจัดการโปรโตคอลความหนาแน่นของตรรกะสูงและความสามารถของ I/O ที่กว้างขวางช่วยให้สามารถรองรับการดำเนินการข้อมูลความเร็วสูงที่ซับซ้อนที่จำเป็นในโครงสร้างพื้นฐานการสื่อสารที่ทันสมัย

ระบบควบคุมอุตสาหกรรม

ในภาคอุตสาหกรรม EP20K100EFC324-1X เก่งในระบบอัตโนมัติความสามารถในการเขียนโปรแกรมและความสามารถในการประมวลผลที่แข็งแกร่งช่วยให้สามารถควบคุมและตรวจสอบได้อย่างแม่นยำเพื่อเพิ่มประสิทธิภาพการดำเนินงานและความน่าเชื่อถือในกระบวนการผลิต

อุปกรณ์อิเล็กทรอนิกส์ยานยนต์

FPGA ทำหน้าที่เป็นส่วนประกอบในแอพพลิเคชั่นยานยนต์โดยเฉพาะอย่างยิ่งในระบบการช่วยเหลือไดรเวอร์ขั้นสูง (ADAS) และระบบ Infotainment ในรถยนต์มันให้กำลังการประมวลผลที่จำเป็นและความสามารถในการปรับตัวเพื่อจัดการข้อมูลและสนับสนุนฟังก์ชันที่ซับซ้อนที่จำเป็นในยานพาหนะสมัยใหม่

อุปกรณ์อิเล็กทรอนิกส์สำหรับผู้บริโภค

เนื่องจากความยืดหยุ่นและประสิทธิภาพสูง EP20K100EFC324-1X ยังพบได้ในอุปกรณ์อิเล็กทรอนิกส์สำหรับผู้บริโภคเช่นโทรทัศน์ความละเอียดสูงและคอนโซลเกมรองรับฟังก์ชั่นที่ซับซ้อนและช่วยในการพัฒนาวงจรการพัฒนาผลิตภัณฑ์ตามความต้องการที่รวดเร็วของตลาดอุปกรณ์อิเล็กทรอนิกส์สำหรับผู้บริโภค

อุปกรณ์การแพทย์

ในสาขาการแพทย์ FPGA นี้มีส่วนช่วยในการทำงานของอุปกรณ์ถ่ายภาพทางการแพทย์และเครื่องมือวินิจฉัยความสามารถในการประมวลผลข้อมูลด้วยความเร็วสูงช่วยให้มั่นใจได้ว่าอุปกรณ์เหล่านี้สามารถให้ผลลัพธ์การวินิจฉัยที่แม่นยำและทันเวลาสำหรับการรักษาและการถ่ายภาพทางการแพทย์ที่มีประสิทธิภาพ

EP20K100EFC324-1X ชิ้นส่วนที่คล้ายกัน

ขั้นตอนการเขียนโปรแกรม EP20K100EFC324-1X

ในการตั้งโปรแกรม EP20K100EFC324-1X อย่างมีประสิทธิภาพซึ่งเป็นสมาชิกของซีรี่ส์ Apex-20KE® FPGA ของ Altera เป็นสิ่งสำคัญที่จะต้องทำตามลำดับขั้นตอนที่มีโครงสร้างกระบวนการนี้ช่วยให้มั่นใจได้ว่าการออกแบบของคุณได้รับการแปลอย่างมีประสิทธิภาพเป็นรูปแบบที่ FPGA สามารถดำเนินการได้ด้านล่างนี้ฉันร่างวิธีการโดยละเอียดในการเขียนโปรแกรมโมเดล FPGA นี้รวมขั้นตอนและการแก้ไขเฉพาะกับอุปกรณ์นี้

1. รายการออกแบบ

เริ่มต้นด้วยการสร้างการออกแบบตรรกะดิจิตอลของคุณใช้ประโยชน์จากฮาร์ดแวร์คำอธิบายภาษา (HDLs) เช่น VHDL หรือ Verilog ซึ่งช่วยให้คุณสามารถอธิบายฟังก์ชั่นฮาร์ดแวร์และตรรกะของระบบของคุณเครื่องมือเช่น Quartus II ของ Altera เสนอสภาพแวดล้อมที่ครอบคลุมสำหรับการเขียนการทดสอบและรวบรวมรหัส HDL ของคุณตรวจสอบให้แน่ใจว่าการออกแบบของคุณเป็นแบบแยกส่วนทำให้ง่ายต่อการดีบักและปรับขนาด

2. การสังเคราะห์

เมื่อรายการการออกแบบของคุณเสร็จสมบูรณ์ขั้นตอนต่อไปคือการสังเคราะห์โดยที่รหัส HDL จะถูกแปลเป็น netlistNetlist นี้แสดงถึงรายการที่เชื่อมต่อระหว่างประตูของประตูรองเท้าแตะและองค์ประกอบฮาร์ดแวร์อื่น ๆ ที่ประกอบขึ้นเป็นการออกแบบของคุณในระหว่างการสังเคราะห์รหัสจะได้รับการปรับให้เหมาะสมสำหรับสถาปัตยกรรมเฉพาะของ EP20K100EFC324-1X เพื่อให้มั่นใจว่าการออกแบบใช้ทรัพยากรของ FPGA อย่างมีประสิทธิภาพเครื่องมือเช่น synplify pro หรือเครื่องมือการสังเคราะห์ภายใน Quartus II สามารถใช้เพื่อจุดประสงค์นี้สิ่งสำคัญคือต้องมุ่งเน้นไปที่การเพิ่มประสิทธิภาพการออกแบบของคุณเพื่อให้ตรงตามเวลาและข้อ จำกัด ด้านทรัพยากร

3. การดำเนินการ

หลังจากการสังเคราะห์การดำเนินการจะเกิดขึ้นขั้นตอนนี้เกี่ยวข้องกับการแมป NetList กับฮาร์ดแวร์ FPGA จริงมันรวมถึงตำแหน่งขององค์ประกอบตรรกะภายใน FPGA และการกำหนดเส้นทางของการเชื่อมต่อระหว่างพวกเขาซอฟต์แวร์ Quartus II อำนวยความสะดวกในกระบวนการนี้ผ่านเครื่องมือการใช้งานซึ่งจัดการตำแหน่งและการกำหนดเส้นทางเพื่อให้ตรงกับความเร็วสัญญาณนาฬิกาที่ต้องการและตัวชี้วัดประสิทธิภาพในระหว่างการใช้งานคุณอาจต้องทำซ้ำการออกแบบของคุณตามข้อเสนอแนะจากเครื่องมือวิเคราะห์เวลาเพื่อให้แน่ใจว่ามีความต้องการประสิทธิภาพทั้งหมด

4. การสร้างบิตสตรีม

หลังจากการใช้งานที่ประสบความสำเร็จขั้นตอนต่อไปจะสร้างบิตสตรีมนี่คือไฟล์ไบนารีที่จะโหลดลงใน FPGABitstream มีข้อมูลที่กำหนดค่าสำหรับทุกองค์ประกอบที่ตั้งโปรแกรมได้ใน FPGA ตั้งค่าอุปกรณ์เพื่อทำหน้าที่ตามการออกแบบของคุณซอฟต์แวร์ Quartus II สามารถสร้างบิตสตรีมนี้ซึ่งพร้อมที่จะดาวน์โหลดไปยัง FPGA

5. การเขียนโปรแกรม FPGA

ขั้นตอนสุดท้ายคือการตั้งโปรแกรม FPGA ด้วยบิตสตรีมที่สร้างขึ้นสิ่งนี้สามารถทำได้โดยใช้โปรแกรมเมอร์ฮาร์ดแวร์ที่เข้ากันได้กับ EP20K100EFC324-1X เช่น USB Blasterเชื่อมต่อโปรแกรมเมอร์เข้ากับบอร์ดการพัฒนาของคุณที่ติดตั้ง FPGA และใช้เครื่องมือโปรแกรมเมอร์ Quartus II เพื่อถ่ายโอนบิตสตรีมไปยัง FPGAขั้นตอนนี้จะโหลดการออกแบบของคุณไปยัง FPGA และจะเริ่มทำงานตามตรรกะที่กำหนดไว้ในรหัส HDL ของคุณ

ข้อดีของ EP20K100EFC324-1X

การบูรณาการสูง

EP20K100EFC324-1X มีความสามารถในการรวมที่สูงเนื่องจากองค์ประกอบตรรกะจำนวนมากและหน่วยความจำฝังตัวการรวมนี้ช่วยให้สามารถรวมฟังก์ชั่นหลายฟังก์ชั่นลงในอุปกรณ์เดียวเป็นผลให้ระบบสามารถทำให้ง่ายขึ้นลดจำนวนส่วนประกอบโดยรวมพื้นที่ทางกายภาพที่จำเป็นและจุดที่อาจเกิดขึ้นของความล้มเหลวในการออกแบบอิเล็กทรอนิกส์

การใช้ตรรกะที่ยืดหยุ่น

สถาปัตยกรรมของ EP20K100EFC324-1X รองรับทั้งตารางค้นหา (LUT) และตรรกะตามผลิตภัณฑ์ความยืดหยุ่นในการใช้ตรรกะนี้ช่วยให้สามารถเพิ่มประสิทธิภาพ FPGA สำหรับแอพพลิเคชั่นที่หลากหลายตั้งแต่ประตูลอจิกแบบง่ายไปจนถึงวงจรผสมที่ซับซ้อนมันให้ข้อได้เปรียบในแง่ของความเก่งกาจในการออกแบบและสามารถรองรับฟังก์ชันการทำงานแบบดิจิตอลได้อย่างกว้างขวาง

โครงสร้างการเชื่อมต่อระหว่างกันขั้นสูง

มีโครงสร้างการเชื่อมต่อระหว่างกันแบบลำดับชั้น FPGA รวมถึงการเชื่อมต่อระหว่างท้องถิ่น, megalab ™และการเชื่อมต่อFastTrack®ทรัพยากรการกำหนดเส้นทางพิเศษเหล่านี้ช่วยเพิ่มประสิทธิภาพการกำหนดเส้นทางสัญญาณและปรับปรุงประสิทธิภาพโดยรวมของอุปกรณ์โครงสร้างการเชื่อมต่อระหว่างกันขั้นสูงนี้เหมาะสำหรับการออกแบบที่ต้องการการส่งข้อมูลความเร็วสูงและเวลาแฝงต่ำทำให้ FPGA เหมาะสำหรับการคำนวณประสิทธิภาพสูงและการสื่อสารโทรคมนาคม

การจัดการนาฬิกา

EP20K100EFC324-1X รวมเทคโนโลยีนาฬิกากลล็อคและ clockboost ซึ่งช่วยในการจัดการนาฬิกาที่มีประสิทธิภาพคุณสมบัติเหล่านี้ช่วยในการรักษาความสมบูรณ์ของสัญญาณนาฬิกาตลอด FPGA ลดความกระวนกระวายใจและปรับปรุงความน่าเชื่อถือของสัญญาณการจัดการนาฬิกาที่มีประสิทธิภาพเป็นสิ่งจำเป็นสำหรับวงจรดิจิตอลแบบซิงโครนัสเพื่อให้มั่นใจว่าการดำเนินงานที่มั่นคงและคาดการณ์ได้ในสภาพแวดล้อมที่หลากหลาย

การออกแบบความยืดหยุ่น

ธรรมชาติที่ตั้งโปรแกรมได้ของ EP20K100EFC324-1X ช่วยให้สามารถปรับฮาร์ดแวร์ให้เข้ากับความต้องการเฉพาะและกำหนดค่า FPGA ใหม่สำหรับแอปพลิเคชันหรือการอัปเดตที่แตกต่างกันความยืดหยุ่นนี้หมายความว่า FPGA เดียวสามารถใช้ในหลายโครงการซึ่งเป็นประโยชน์ในภูมิทัศน์ทางเทคโนโลยีแบบไดนามิกที่ความต้องการสามารถเปลี่ยนแปลงได้อย่างรวดเร็ว

การสร้างต้นแบบอย่างรวดเร็ว

FPGAs เช่น EP20K100EFC324-1X เปิดใช้งานการสร้างต้นแบบอย่างรวดเร็วของวงจรดิจิตอลคุณสามารถพัฒนาและทำซ้ำการออกแบบได้อย่างรวดเร็วโดยไม่ต้องใช้เวลานำที่ยาวนานซึ่งเกี่ยวข้องกับการพัฒนา ASIC แบบกำหนดเองความสามารถในการสร้างแบบจำลองและทดสอบการออกแบบใหม่อย่างรวดเร็วช่วยเร่งกระบวนการพัฒนาซึ่งนำไปสู่นวัตกรรมที่เร็วขึ้นและเวลาในการตลาดที่สั้นลง

ประสิทธิภาพต้นทุน

การรวมฟังก์ชั่นหลายฟังก์ชั่นภายใน FPGA เดียวช่วยลดความต้องการส่วนประกอบที่ไม่ต่อเนื่องเพิ่มเติมซึ่งสามารถนำไปสู่การประหยัดต้นทุนทั้งในการจัดซื้อและการประกอบการรวมนี้ยังช่วยลดความซับซ้อนของกระบวนการผลิตและสามารถลดความซับซ้อนของระบบโดยรวมซึ่งนำไปสู่การบำรุงรักษาที่ลดลงและการอัพเกรดค่าใช้จ่ายผ่านวงจรชีวิตของผลิตภัณฑ์

การสนับสนุนระยะยาว

ด้านที่กำหนดค่าใหม่ของ EP20K100EFC324-1X ทำให้มั่นใจได้ว่าฮาร์ดแวร์สามารถอัปเดตเพื่อแก้ไขข้อบกพร่องปรับปรุงประสิทธิภาพหรือเพิ่มคุณสมบัติใหม่โดยไม่ต้องเปลี่ยนฮาร์ดแวร์ทางกายภาพการสนับสนุนและการปรับตัวในระยะยาวนี้ช่วยปกป้องการลงทุนและช่วยให้อุปกรณ์มีความเกี่ยวข้องเมื่อมาตรฐานและเทคโนโลยีใหม่เกิดขึ้น

ขนาดบรรจุภัณฑ์ EP20K100EFC324-1X

EP20K100EFC324-1X เป็น FPGA จากซีรี่ส์ Apex-20KE®ของ Altera ซึ่งตั้งอยู่ในก 324-ball Fine-Pitch Ball Grid Array (FBGA) บรรจุุภัณฑ์.ขนาดบรรจุภัณฑ์มีดังนี้:

- ขว้าง: 1 มม.

- ความยาว×กว้าง: 19 มม. × 19 มม.

- พื้นที่: 361 mm²

ผู้ผลิต EP20K100EFC324-1X

EP20K100EFC324-1X เป็นแบบจำลองจาก Apex-20KE® Series ของอาร์เรย์ประตูที่ตั้งโปรแกรมได้ (FPGAs) ซึ่งพัฒนาโดย Alteraหลังจากการเข้าซื้อกิจการของ Intel ในปี 2558 FPGA และผลิตภัณฑ์ Altera อื่น ๆ นี้กลายเป็นส่วนหนึ่งของพอร์ตโซลูชั่นโซลูชั่นที่สามารถตั้งโปรแกรมได้ของ Intelเป็นผลให้ Intel ยังคงสนับสนุนสายผลิตภัณฑ์ของ Altera ในขณะที่รวมเข้ากับการนำเสนอเทคโนโลยีขั้นสูงของตนเองแม้ว่า EP20K100EFC324-1X ได้รับการจัดประเภทว่าล้าสมัยและไม่ได้ผลิตอีกต่อไป แต่มรดกของมันจะถูกเก็บรักษาไว้ภายใต้ Intel ซึ่งแนะนำรุ่น FPGA รุ่นใหม่สำหรับแอปพลิเคชันปัจจุบันเพื่อให้แน่ใจว่าการสนับสนุนและความพร้อมใช้งานในระยะยาว

บทสรุป

EP20K100EFC324-1X เป็น FPGA ที่ทรงพลังและยืดหยุ่นที่อนุญาตให้สร้างและทดสอบวงจรดิจิตอลที่กำหนดเองมันให้ประสิทธิภาพสูงหน่วยความจำในตัวและการสนับสนุนหลายแรงดันทำให้มีประโยชน์ในหลายอุตสาหกรรมคู่มือนี้นำคุณผ่านคุณสมบัติหลักการออกแบบและขั้นตอนในการตั้งโปรแกรม FPGA นี้อย่างง่าย ๆ เพื่อให้คุณสามารถเข้าใจและใช้งานได้ง่าย

PDF แผ่นข้อมูล

ข้อมูล EP20K100EFC324-1X:

เกี่ยวกับเรา

ALLELCO LIMITED

อ่านเพิ่มเติม

สอบถามรายละเอียดเพิ่มเติมอย่างรวดเร็ว

กรุณาส่งคำถามเราจะตอบกลับทันที

คำถามที่พบบ่อย [FAQ]

1. EP20K100EFC324-1X เปรียบเทียบกับรุ่น FPGA รุ่นใหม่ได้อย่างไร

EP20K100EFC324-1X ยังคงเป็น FPGA ที่ทรงพลังสำหรับระบบดั้งเดิมและแอพพลิเคชั่นอุตสาหกรรมที่ต้องใช้ความหนาแน่นของตรรกะสูงและความสามารถ I/O ที่ยืดหยุ่นอย่างไรก็ตามเมื่อเปรียบเทียบกับ FPGA ที่ทันสมัยเช่นซีรีส์ไซโคลนของ Intel, Arria หรือ Stratix ซีรีย์มันขาดประสิทธิภาพการใช้พลังงานขั้นสูงเครื่องรับส่งสัญญาณความเร็วสูงและการเร่งความเร็วที่ขับเคลื่อนด้วย AIหากคุณกำลังออกแบบระบบใหม่เราสามารถแนะนำรุ่นที่เทียบเท่าหรืออัพเกรด

2. EP20K100EFC324-1X รองรับอินเตอร์เฟสหน่วยความจำภายนอกเช่น DDR หรือ SRAM หรือไม่?

ใช่ EP20K100EFC324-1X รองรับอินเตอร์เฟสหน่วยความจำภายนอกรวมถึง SRAM และ SDRAMอย่างไรก็ตามมันไม่สนับสนุน DDR2/DDR3หากจำเป็นต้องมีการเชื่อมต่อหน่วยความจำความเร็วสูงอาจจำเป็นต้องใช้ตรรกะภายนอกเพิ่มเติมหรือ FPGA ที่ใหม่กว่า

3. ฉันสามารถกำหนดค่า EP20K100EFC324-1X ได้หลายครั้งได้ไหม

ใช่เช่นเดียวกับ FPGA ทั้งหมดอุปกรณ์นี้สามารถ reprogrammable ได้อย่างสมบูรณ์อย่างไรก็ตามหากใช้การกำหนดค่าที่ผันผวนคุณจะต้องมีหน่วยความจำภายนอก (เช่น PROM อนุกรม) เพื่อรักษาการออกแบบหลังจากการปั่นจักรยาน

4. ฉันสามารถตั้งโปรแกรม EP20K100EFC324-1X โดยใช้ซอฟต์แวร์ Intel Quartus ได้หรือไม่?

ใช่คุณสามารถตั้งโปรแกรม EP20K100EFC324-1X โดยใช้ Intel Quartus II (รุ่น Legacy) เนื่องจาก FPGA นี้เป็นของตระกูล Apex-20KE®ตรวจสอบให้แน่ใจว่าเวอร์ชัน Quartus II ของคุณรองรับอุปกรณ์นี้เนื่องจาก Quartus Prime Editions รุ่นใหม่ไม่รองรับ FPGA แบบดั้งเดิม

5. ข้อกำหนดด้านแหล่งจ่ายไฟควรพิจารณาเมื่อใช้ EP20K100EFC324-1X

EP20K100EFC324-1X ทำงานด้วยช่วงแรงดันไฟฟ้าแกน 1.71V ถึง 1.89Vนอกจากนี้ยังมีเทคโนโลยี Multivolt ™ I/O ซึ่งรองรับระดับตรรกะ 1.8V, 2.5V, 3.3V และ 5.0Vตรวจสอบให้แน่ใจว่าแหล่งจ่ายไฟของคุณตรงตามข้อกำหนดของแรงดันไฟฟ้าเหล่านี้เพื่อประสิทธิภาพที่มั่นคง

XCV200-6FG456C FPGA: คุณสมบัติข้อมูลจำเพาะการเขียนโปรแกรมและแอปพลิเคชัน

บน 20/03/2025

ทำไม 0603 ส่วนประกอบจึงเป็นที่นิยมในอิเล็กทรอนิกส์สมัยใหม่

บน 20/03/2025

โพสต์ยอดนิยม

-

คอมพิวเตอร์ชุดคำสั่งที่ซับซ้อน: พวกเขาเปลี่ยนการคำนวณอย่างไร?

บน 18/04/8000 147770

-

USB-C Pinout และคุณสมบัติ

บน 18/04/2000 112006

-

การใช้ Xilinx Unified Simulation Primitives: คู่มือที่ครอบคลุมสำหรับการออกแบบและการจำลอง FPGA

บน 18/04/1600 111351

-

การทำความเข้าใจแรงดันไฟฟ้าของแหล่งจ่ายไฟในอิเล็กทรอนิกส์ VCC, VDD, VEE, VSS และ GND

บน 18/04/0400 83768

-

คู่มือเชื่อมต่อ RJ45: Pinout, การเดินสาย, ประเภทสายเคเบิลและการใช้งาน

บน 01/01/1970 79562

-

คู่มือที่ดีที่สุดสำหรับรหัสสีลวดในระบบไฟฟ้าที่ทันสมัย

วิธีที่ระบบไฟฟ้าของเราใช้สีไม่ได้มีไว้สำหรับรูปลักษณ์ตอนนี้สีลวดแต่ละอันบ่งบอกถึงฟังก์ชั่นเฉพาะทำให้ง่ายต่อการระบุและจัดการส่วนประกอบไฟฟ้าอย่างถูกต้องระหว่างการติดตั้งและบำรุงรักษาสิ่งนี้ไม่เพียง แ...บน 01/01/1970 66959

-

คู่มือการล้างวาล์ว: ฟังก์ชั่นอาการการทดสอบและการเปลี่ยนประสิทธิภาพของเครื่องยนต์ที่ดีที่สุด

วาล์วล้างเป็นส่วนสำคัญของระบบรถยนต์ที่ช่วยให้อากาศสะอาดโดยการจัดการไอระเหยเชื้อเพลิงก่อนที่พวกเขาจะสามารถหลบหนีไปสู่ชั้นบรรยากาศได้สิ่งนี้ไม่เพียง แต่ช่วยสิ่งแวดล้อมด้วยการลดมลพิษ แต่ยังทำให้รถทำงา...บน 01/01/1970 63098

-

คุณภาพ (q) ปัจจัย: สมการและแอปพลิเคชัน

ปัจจัยด้านคุณภาพหรือ 'Q' เป็นสิ่งสำคัญเมื่อตรวจสอบว่าตัวเหนี่ยวนำและ resonators ทำงานได้ดีเพียงใดในระบบอิเล็กทรอนิกส์ที่ใช้ความถี่วิทยุ (RF)'Q' วัดว่าวงจรช่วยลดการสูญเสียพลังงานและส่งผลกระทบต่อช่วง...บน 01/01/1970 63040

-

บรรลุประสิทธิภาพสูงสุดด้วยทฤษฎีการถ่ายโอนพลังงานสูงสุด

ทฤษฎีบทการถ่ายโอนพลังงานสูงสุดอธิบายว่าพลังงานจากแหล่งกำเนิดเช่นแบตเตอรี่หรือเครื่องกำเนิดไฟฟ้าจะไหลไปยังโหลดที่เชื่อมต่อได้อย่างไรมันแสดงเงื่อนไขที่แน่นอนที่โหลดได้รับพลังงานมากที่สุดบทความนี้ครอบ...บน 01/01/1970 54095

-

ข้อมูลจำเพาะและความเข้ากันได้ของแบตเตอรี่ A23

แบตเตอรี่ A23 เป็นแบตเตอรี่รูปทรงกระบอกขนาดเล็กที่มีแรงดันไฟฟ้าสูงเรียกอีกอย่างว่า 23A, 23AE หรือ MN21 มันทำงานที่ 12 โวลต์และสูงกว่าแบตเตอรี่ AA หรือ AAA มากการออกแบบพิเศษทำให้เหมาะสำหรับ...บน 01/01/1970 52182