ทำความเข้าใจกับคุณสมบัติ AD9959 สำหรับการประมวลผลสัญญาณ

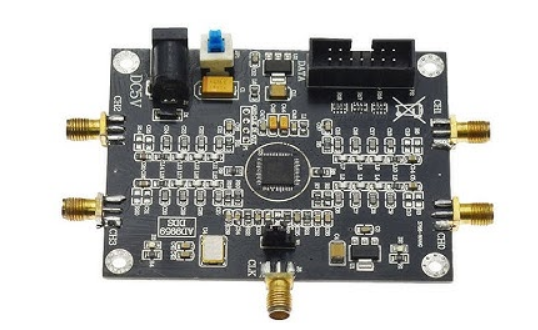

AD9959 เป็นซินธิไซเซอร์ดิจิตอลที่ทรงพลังและยืดหยุ่นซึ่งให้การควบคุมความถี่เฟสและแอมพลิจูดในสี่ช่องทางอิสระบทความนี้ครอบคลุมคุณสมบัติที่สำคัญข้อกำหนดทางเทคนิคและแอพพลิเคชั่นทั่วไปของ AD9959 ทำให้คุณเข้าใจได้ง่ายขึ้นว่าอุปกรณ์นี้สามารถใช้งานในการตั้งค่าต่างๆได้อย่างไรไม่ว่าคุณจะต้องการสร้างออสซิลเลเตอร์ท้องถิ่นที่คล่องตัวหรือซิงโครไนซ์ระบบที่ซับซ้อนเช่นเรดาร์อาร์เรย์แบบเฟส AD9959 ให้ความแม่นยำและการปรับตัวที่จำเป็นสำหรับโครงการที่หลากหลายในตอนท้ายของคู่มือนี้คุณจะมีความเข้าใจที่ชัดเจนว่า AD9959 ทำงานอย่างไรและสามารถนำไปใช้ในสาขาต่าง ๆ ได้อย่างไรแคตตาล็อก

ภาพรวมของ AD9959

ที่ Ad9959 เสนอแกนสังเคราะห์ดิจิตอลโดยตรงสี่แกนช่วยให้คุณสามารถควบคุมความถี่เฟสและแอมพลิจูดได้อย่างอิสระสำหรับแต่ละช่องด้วยความสามารถในการจัดการการมอดูเลตสูงสุด 16 ระดับไม่ว่าจะเป็นความถี่เฟสหรือแอมพลิจูดมันจะนำความยืดหยุ่นมาสู่การออกแบบของคุณเนื่องจากช่องทั้งหมดแบ่งปันนาฬิการะบบเดียวกันพวกเขาจะยังคงซิงโครไนซ์เพื่อให้มั่นใจว่าการทำงานที่ราบรื่นในหลายช่องทางยิ่งกว่านั้นหากคุณทำงานกับ AD9959 มากกว่าหนึ่งตัวคุณสามารถซิงโครไนซ์อุปกรณ์หลายตัวได้อย่างง่ายดายทำให้เหมาะสำหรับการตั้งค่าที่ซับซ้อน

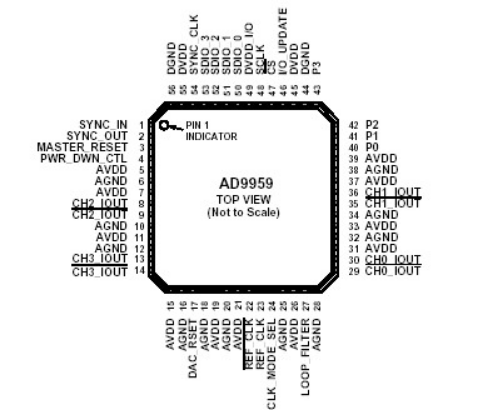

Ad9959 แผนภาพ Pinout

| หมายเลขพิน | ของช่วยในการจำ | I/O | คำอธิบาย |

| 1 | sync_in | ฉัน | ใช้เพื่อซิงโครไนซ์อุปกรณ์ AD9959 หลายตัวเชื่อมต่อกับพิน sync_out ของอุปกรณ์หลัก AD9959 |

| 2 | sync_out | โอ | ใช้เพื่อซิงโครไนซ์อุปกรณ์ AD9959 หลายตัวเชื่อมต่อกับพิน sync_in ของอุปกรณ์ Slave AD9959 |

| 3 | master_reset | ฉัน | พินรีเซ็ตสูงที่ใช้งานอยู่การยืนยัน PIN master_reset บังคับให้ลงทะเบียนภายใน AD9959 ไปยังสถานะเริ่มต้นของพวกเขา |

| 4 | pwr_dwn_ctl | ฉัน | การควบคุมพลังงานภายนอก |

| 5, 7, 11, 15, 19, 21, 26, 31, 33, 37, 39 | AVDD | ฉัน | หมุดแหล่งจ่ายไฟแบบอะนาล็อก (1.8V) |

| 6, 10, 12, 16, 18, 20, 25, 28, 32, 34, 38 | agnd | ฉัน | หมุดกราวด์แบบอะนาล็อก |

| 44, 56 | ดีวีดี | ฉัน | หมุดแหล่งจ่ายไฟดิจิตอล (1.8V) |

| 45, 55 | dgnd | ฉัน | หมุดพื้นดินดิจิตอล |

| 8 | ch2_iout | โอ | เอาต์พุต DAC จริงสิ้นสุดลงใน AVDD |

| 9 | ch2_iout | โอ | เอาท์พุท DAC เสริมสิ้นสุดลงใน AVDD |

| 13 | ch3_iout | โอ | เอาต์พุต DAC จริงสิ้นสุดลงใน AVDD |

| 14 | ch3_iout | โอ | เอาท์พุท DAC เสริมสิ้นสุดลงใน AVDD |

| 17 | dac_rset | ฉัน | สร้างกระแสอ้างอิงสำหรับ DAC ทั้งหมดตัวต้านทาน 1.91 kΩ (เล็กน้อย) เชื่อมต่อจาก PIN 17 ถึง AGND |

| 22 | ref_clk | ฉัน | นาฬิกาอ้างอิงเสริม/อินพุตออสซิลเลเตอร์เมื่อ ref_clk ทำงานในโหมดปลายเดี่ยวพินนี้ควรจะถูกแยกออกเป็น avdd หรือ agnd ด้วยตัวเก็บประจุ 0.1 µF |

| 23 | ref_clk | ฉัน | นาฬิกาอ้างอิง/อินพุตออสซิลเลเตอร์เมื่อ ref_clk ทำงานในโหมดปลายเดี่ยวนี่คืออินพุตดูส่วนโหมดการทำงานสำหรับการกำหนดค่านาฬิกาอ้างอิง |

| หมายเลขพิน | ของช่วยในการจำ | I/O | คำอธิบาย |

| 24 | clk_mode_sel | ฉัน | พินควบคุมสำหรับส่วนออสซิลเลเตอร์ข้อควรระวัง: อย่าขับพินนี้เกิน 1.8Vเมื่อสูง (1.8V) ส่วนออสซิลเลเตอร์จะเปิดใช้งานเพื่อรับคริสตัลเป็นแหล่ง ref_clkเมื่อต่ำส่วนออสซิลเลเตอร์จะถูกข้าม |

| 27 | loop_filter | ฉัน | เชื่อมต่อกับเครือข่ายการชดเชยศูนย์ภายนอกของตัวกรองลูป PLLโดยทั่วไปแล้วเครือข่ายจะประกอบด้วยตัวต้านทาน0Ωในซีรีย์ที่มีตัวเก็บประจุ 680pF เชื่อมโยงกับ AVDD |

| 29 | ch0_iout | โอ | เอาท์พุท DAC เสริมสิ้นสุดลงใน AVDD |

| 30 | ch0_iout | โอ | เอาต์พุต DAC จริงสิ้นสุดลงใน AVDD |

| 35 | ch1_iout | โอ | เอาท์พุท DAC เสริมสิ้นสุดลงใน AVDD |

| 36 | ch1_iout | โอ | เอาต์พุต DAC จริงสิ้นสุดลงใน AVDD |

| 40 ถึง 43 | P0 ถึง P3 | ฉัน | หมุดข้อมูลที่ใช้สำหรับการมอดูเลต (FSK, PSK, ASK) เพื่อเริ่ม/หยุดการสะสมของการกวาดหรือใช้เพื่อเพิ่มขึ้น/ลาดลงแอมพลิจูดเอาท์พุทข้อมูลเป็นแบบซิงโครนัสกับ sync_clk (พิน 54)อินพุตข้อมูลจะต้องตรงตามข้อกำหนดการตั้งค่าและค้างไว้เวลาของ SYNC_CLKฟังก์ชั่นของพินเหล่านี้ถูกควบคุมโดยบิตการกำหนดค่าพินโปรไฟล์ (PPC) บิต (FR1 [14:12]) |

| 46 | i/o_update | ฉัน | ขอบที่เพิ่มขึ้นถ่ายโอนข้อมูลจากบัฟเฟอร์พอร์ต I/O อนุกรมไปยังการลงทะเบียนที่ใช้งานอยู่I/O_UPDATE เป็นซิงโครนัสกับ SYNC_CLK (PIN 54)I/O_UPDATE จะต้องเป็นไปตามข้อกำหนดการตั้งค่าและเวลาค้างไว้ของ SYNC_CLK เพื่อรับประกันความล่าช้าไปป์ไลน์คงที่ของข้อมูลไปยังเอาต์พุต DAC;มิฉะนั้นจะมีระยะเวลา± 1 sync_clk ของความไม่แน่นอนไปป์ไลน์ความกว้างของพัลส์ขั้นต่ำคือช่วงเวลาหนึ่ง SYNC_CLK |

| 47 | CS \ | ฉัน | เลือกชิปต่ำที่ใช้งานอยู่อนุญาตให้อุปกรณ์หลายเครื่องแบ่งปัน I/O Bus (SPI) ทั่วไป |

| 48 | SCLK | ฉัน | นาฬิกาข้อมูลอนุกรมสำหรับการดำเนินการ I/Oบิตข้อมูลถูกเขียนขึ้นที่ขอบที่เพิ่มขึ้นของ SCLK และอ่านที่ขอบที่ตกลงมาของ SCLK |

| 49 | dvdd_i/o | ฉัน | แหล่งจ่ายไฟดิจิตอล 3.3V สำหรับพอร์ต SPI และ Digital I/O |

| 50 | SDIO_0 | I/O | Data Pin SDIO_0 อุทิศให้กับพอร์ตอนุกรม I/O เท่านั้น |

| 51, 52 | SDIO_1, SDIO_2 | I/O | Data Pin SDIO_1 และ Data PIN SDIO_2 สามารถใช้สำหรับพอร์ต I/O อนุกรมหรือใช้เพื่อเริ่มต้นทางลาด/ทางลาด (RU/RD) ของแอมพลิจูดเอาต์พุต DAC |

| 53 | SDIO_3 | I/O | Data Pin SDIO_3 สามารถใช้สำหรับพอร์ต I/O อนุกรมหรือเพื่อเริ่มต้น Ramp-Up/Ramp-Down (RU/RD) ของแอมพลิจูดเอาท์พุท DACในโหมดเดี่ยวหรือ 2 บิต SDIO_3 ใช้สำหรับ SYNC_I/Oหากไม่ได้ใช้ฟังก์ชั่น SYNC_I/O ให้ผูกเข้ากับกราวด์หรือตรรกะ 0 อย่าปล่อยให้ SDIO_3 ลอยอยู่ในโหมดบิตเดี่ยวหรือ 2 บิต |

| 54 | sync_clk | โอ | SYNC_CLK ทำงานที่หนึ่งในสี่อัตรานาฬิการะบบมันสามารถปิดใช้งานได้I/O_UPDATE หรือข้อมูล (PIN 40 ถึง PIN 43) เป็นซิงโครนัสกับ SYNC_CLKในการรับประกันความล่าช้าไปป์ไลน์คงที่ของข้อมูลไปยังเอาท์พุท DAC, I/O_UPDATE หรือข้อมูล (PIN 40 ถึง PIN 43) จะต้องตรงตามข้อกำหนดการตั้งค่าและเวลาค้างไว้ที่ขอบที่เพิ่มขึ้นของ SYNC_CLK;มิฉะนั้น± 1 sync_clk ระยะเวลาของความไม่แน่นอนเกิดขึ้น |

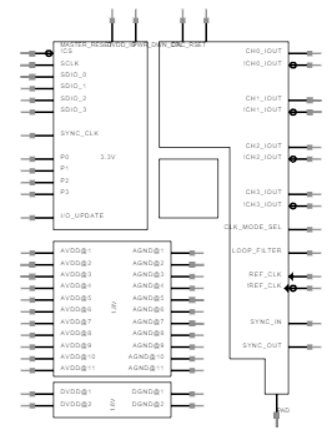

AD9959 ภาพรวมโมเดล CAD

Ad9959 สัญลักษณ์

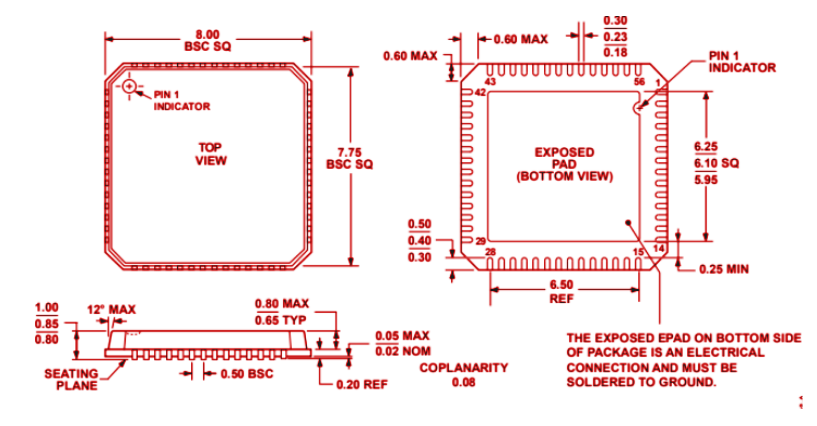

Ad9959 รอยเท้า

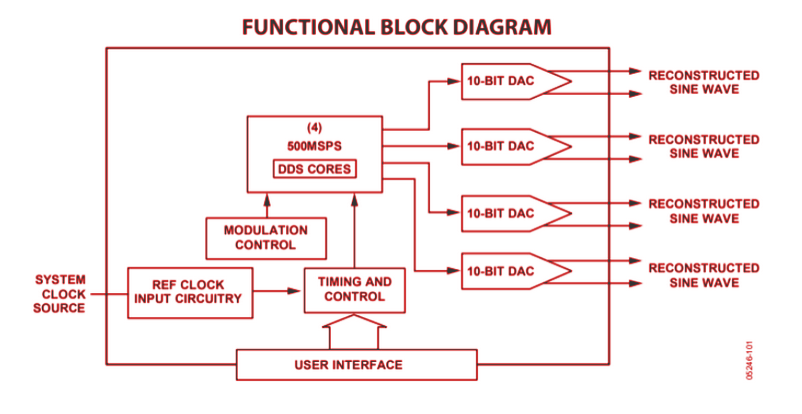

รายละเอียด AD9959 บล็อกไดอะแกรม

ข้อมูลจำเพาะทางเทคนิคของ AD9959

ข้อมูลจำเพาะทางเทคนิคแอตทริบิวต์พารามิเตอร์และส่วนที่เทียบเคียงได้สำหรับ ANALOG Devices Inc. AD9959BCPZ

| พิมพ์ | พารามิเตอร์ |

| สถานะวงจรชีวิต | |

| เวลานำโรงงาน | 8 สัปดาห์ |

| ติดต่อชุบ | ดีบุก |

| ติดตั้ง | ติดตั้งพื้นผิว |

| ประเภทการติดตั้ง | ติดตั้งพื้นผิว |

| แพ็คเกจ / เคส | 56-VFQFN ที่เปิดเผย Pad, CSP |

| จำนวนพิน | 56 |

| อุณหภูมิการทำงาน | -40 ° C ถึง 85 ° C |

| การบรรจุหีบห่อ | ถาด |

| รหัส JESD-609 | E3 |

| รหัส pbfree | เลขที่ |

| สถานะชิ้นส่วน | คล่องแคล่ว |

| ระดับความไวต่อความชื้น (MSL) | 3 (168 ชั่วโมง) |

| จำนวนการยุติ | 56 |

| การเลิก | SMD/SMT |

| รหัส ECCN | หู 99 |

| คุณสมบัติเพิ่มเติม | ยังต้องมีการจัดหา 3.3V |

| การกระจายพลังงานสูงสุด | 680MW |

| แรงดันไฟฟ้า - อุปทาน | 1.71V ถึง 1.96V |

| ตำแหน่งเทอร์มินัล | รูปสี่เหลี่ยม |

| รูปแบบเทอร์มินัล | ไม่มีตะกั่ว |

| อุณหภูมิรีดคืนสูงสุด (° C) | 260 |

| แรงดันไฟฟ้า | 1.8V |

| สนามเทอร์มินัล | 0.5 มม. |

| ความถี่ | 500MHz |

| Time @ peak reflow temp (s) | 30 |

| หมายเลขชิ้นส่วนฐาน | Ad9959 |

| จำนวนพิน | 56 |

| สถานะคุณสมบัติ | ไม่ผ่านการคัดเลือก |

| แรงดันไฟฟ้า | 1.8V |

| ส่วนต่อประสาน | เป็นลำดับ |

| กระแสการดำเนินงานปัจจุบัน | 180ma |

| แหล่งจ่ายไฟเล็กน้อย | 160ma |

| กระแสไฟสูงสุด | 185ma |

| ประเภท UPS/UCS/อุปกรณ์ต่อพ่วง ICS | |

| จำนวนบิต | 10 |

| อัตราการสุ่มตัวอย่าง | 500 msps |

| การสแกนขอบเขต | เลขที่ |

| โหมดพลังงานต่ำ | ใช่ |

| อัตราการแปลง | 500 msps |

| จำนวนตัวแปลง D/A | 4 |

| ความละเอียด (บิต) | 10 b |

| การปรับความกว้างคำ (บิต) | 32 b |

| ความสูง | 830μm |

| ความยาว | 8 มม. |

| ความกว้าง | 8 มม. |

| ไปถึง SVHC | ไม่มี SVHC |

| สถานะ ROHS | Rohs3 เป็นไปตามมาตรฐาน |

| นำฟรี | มีตะกั่ว |

Ad9959 คุณสมบัติที่สำคัญ

4 ช่อง DDS ที่ซิงโครไนซ์ที่ 500 msps

AD9959 ให้ช่องทาง Direct Digital Synthesizer (DDS) แบบซิงโครไนซ์สี่ช่องซึ่งทำงานได้สูงสุด 500 mSpsสิ่งนี้ช่วยให้คุณสร้างสัญญาณที่แม่นยำในหลายช่องทางในขณะที่ยังคงรักษาซิงโครไนซ์ซึ่งมีประโยชน์อย่างยิ่งเมื่อทำงานในโครงการที่ต้องใช้เอาต์พุตหลายรายการทำงานร่วมกันอย่างราบรื่น

การควบคุมความถี่อิสระเฟสและแอมพลิจูด

ช่อง DDS ทั้งสี่ช่องแต่ละช่องมีการควบคุมความถี่เฟสและแอมพลิจูดที่เป็นอิสระสิ่งนี้ช่วยให้คุณปรับแต่งแต่ละช่องให้เหมาะกับความต้องการที่แตกต่างกันทำให้คุณมีความยืดหยุ่นในการจัดการพารามิเตอร์สัญญาณต่างๆ

เวลาแฝงที่ตรงกันสำหรับการเปลี่ยนแปลงความถี่เฟสและแอมพลิจูด

AD9959 ทำให้มั่นใจได้ว่าการเปลี่ยนแปลงความถี่เฟสและแอมพลิจูดจะถูกซิงโครไนซ์ข้ามช่องทางซึ่งหมายความว่าเมื่อคุณปรับพารามิเตอร์หนึ่งการเปลี่ยนแปลงจะเกิดขึ้นพร้อมกันในทุกช่องทางช่วยให้คุณรักษาเอาต์พุตที่สอดคล้องกันโดยไม่ต้องล่าช้า

การแยกช่องไปยังช่องทางที่ยอดเยี่ยม

ด้วยการแยกช่องทางไปยังช่องทางมากกว่า 65 เดซิเบล AD9959 จะช่วยลดการรบกวนระหว่างช่องทางสิ่งนี้ทำให้มั่นใจได้ว่าสัญญาณที่สร้างขึ้นในแต่ละช่องนั้นสะอาดและชัดเจนให้ประสิทธิภาพที่มีคุณภาพสูงขึ้นในการออกแบบของคุณ

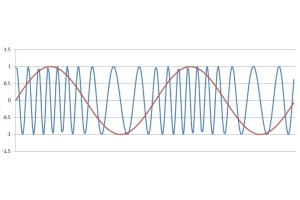

ความสามารถในการกวาดเชิงเส้น

AD9959 รองรับความถี่เชิงเส้นเฟสและแอมพลิจูดคุณลักษณะนี้ช่วยให้คุณสามารถเปลี่ยนค่าได้อย่างราบรื่นระหว่างค่าทำให้ง่ายต่อการสร้างสัญญาณที่ค่อยๆเปลี่ยนไปตามกาลเวลาซึ่งอาจเป็นประโยชน์สำหรับการทดสอบและการสอบเทียบ

การปรับความถี่สูงถึง 16 ระดับเฟสและแอมพลิจูด

อุปกรณ์สามารถจัดการการมอดูเลตสูงสุด 16 ระดับสำหรับความถี่เฟสหรือแอมพลิจูดความยืดหยุ่นในระดับนี้ช่วยให้คุณสามารถใช้แผนการมอดูเลตที่หลากหลายตั้งแต่ง่ายไปจนถึงความซับซ้อนขึ้นอยู่กับความต้องการโครงการของคุณ

ตัวแปลงดิจิตอลถึงอะนาล็อก 10 บิต (DACs)

แต่ละช่องมาพร้อมกับ DAC แบบ 10 บิตแบบรวมของตัวเองช่วยให้คุณสามารถแปลงสัญญาณดิจิตอลเป็นเอาต์พุตอะนาล็อกได้อย่างแม่นยำสิ่งนี้ทำให้ AD9959 เป็นตัวเลือกที่ยอดเยี่ยมเมื่อคุณต้องการการสร้างสัญญาณอะนาล็อกที่แม่นยำในรูปแบบกะทัดรัด

กระแสเต็มรูปแบบ DAC ที่ตั้งโปรแกรมได้เป็นรายบุคคล

คุณสามารถตั้งโปรแกรมกระแสเต็มรูปแบบสำหรับ DAC แต่ละตัวแยกกันซึ่งช่วยให้คุณควบคุมกำลังขับของแต่ละช่องการปรับแต่งระดับนี้ช่วยให้คุณสามารถเพิ่มประสิทธิภาพระดับพลังงานสำหรับช่องทางที่แตกต่างกันตามข้อกำหนดเฉพาะของคุณ

ความละเอียดการปรับความถี่ละเอียด

AD9959 มีความละเอียดการปรับจูน 0.12 Hz หรือดีกว่าให้การควบคุมที่แม่นยำเกี่ยวกับความถี่ของสัญญาณที่คุณสร้างขึ้นความแม่นยำในระดับนี้มีประโยชน์เมื่อทำงานกับแอปพลิเคชันที่การปรับความถี่เล็กน้อยสร้างความแตกต่างอย่างมาก

ชดเชยเฟสความละเอียดสูง

ด้วยความละเอียดชดเชยระยะ 14 บิต AD9959 ช่วยให้คุณปรับแต่งเฟสของแต่ละช่องคุณลักษณะนี้มีประโยชน์เมื่อคุณต้องการการปรับเฟสที่แน่นอนระหว่างสัญญาณเช่นเมื่อจัดตำแหน่งหลายสัญญาณในระบบอาเรย์แบบเฟส

การปรับขนาดแอมพลิจูดเอาท์พุท

AD9959 ให้ความละเอียดการปรับขนาดแอมพลิจูดแบบเอาท์พุท 10 บิตสิ่งนี้ช่วยให้คุณสามารถปรับแอมพลิจูดเอาต์พุตด้วยความแม่นยำสูงทำให้คุณมีความยืดหยุ่นในการควบคุมความแรงของสัญญาณได้อย่างแม่นยำยิ่งขึ้น

อินเทอร์เฟซพอร์ต I/O แบบอนุกรม

อินเทอร์เฟซพอร์ต I/O แบบอนุกรม (SPI) เสนอปริมาณงานที่ได้รับการปรับปรุงให้คุณถ่ายโอนข้อมูลได้อย่างรวดเร็วและมีประสิทธิภาพระหว่างอุปกรณ์และระบบของคุณสิ่งนี้จะเพิ่มความเร็วในการสื่อสารซึ่งมีประโยชน์ในแอปพลิเคชันที่รวดเร็ว

การควบคุมพลังงานลง

AD9959 มีทั้งตัวเลือกซอฟต์แวร์และฮาร์ดแวร์สำหรับการเปิดเครื่องทำให้คุณควบคุมวิธีการประหยัดพลังงานได้อย่างไรคุณสมบัตินี้มีประโยชน์อย่างยิ่งในการออกแบบที่ใส่ใจพลังงานซึ่งประสิทธิภาพการใช้พลังงานเป็นสิ่งสำคัญ

การดำเนินการจัดหาคู่

อุปกรณ์ทำงานด้วยระบบการจัดหาคู่: 1.8 V สำหรับ DDS Core และ 3.3 V สำหรับ Serial I/Oการกำหนดค่านี้ช่วยให้ประสิทธิภาพสมดุลกับความต้องการพลังงานทำให้สามารถปรับให้เข้ากับสภาพแวดล้อมการออกแบบที่หลากหลาย

การซิงโครไนซ์อุปกรณ์หลายตัว

AD9959 รองรับการซิงโครไนซ์ในหลาย ๆ อุปกรณ์ช่วยให้คุณสามารถขยายการออกแบบของคุณด้วยหน่วยเพิ่มเติมในขณะที่รักษาเวลาที่แม่นยำระหว่างพวกเขาสิ่งนี้ทำให้ง่ายต่อการขยายโครงการของคุณโดยไม่สูญเสียการซิงโครไนซ์

ตัวคูณ REFCLK ที่เลือกได้

ด้วยตัวคูณ RefCLK ที่เลือกได้ตั้งแต่ 4 ×ถึง 20 × AD9959 นำเสนอความยืดหยุ่นในตัวเลือกการตอกบัตรช่วยให้คุณเลือกการตั้งค่าที่ดีที่สุดสำหรับการออกแบบของคุณ

REFCLK Crystal Oscillator ในตัว

อุปกรณ์ดังกล่าวรวมถึง roscillator refclk crystal ในตัวซึ่งทำให้กระบวนการออกแบบของคุณง่ายขึ้นโดยการลดความต้องการส่วนประกอบภายนอกทำให้ง่ายต่อการจัดการเวลาภายในระบบ

แพ็คเกจ LFCSP ขนาดกะทัดรัด 56

AD9959 มาในแพ็คเกจ LFCSP 56-lead ซึ่งให้ตัวเลือกขนาดกะทัดรัดและประหยัดพื้นที่สำหรับการรวมช่อง DDS หลายช่องเข้ากับการออกแบบของคุณปัจจัยขนาดเล็กนี้เหมาะอย่างยิ่งเมื่อคุณต้องการฟังก์ชั่นสูงโดยไม่ต้องใช้พื้นที่บอร์ดมากเกินไป

แอปพลิเคชัน AD9959 ทั่วไป

ออสซิลเลเตอร์ท้องถิ่นว่องไว

AD9959 เหมาะสำหรับการใช้งานในออสซิลเลเตอร์ท้องถิ่นที่คล่องตัวให้การควบคุมที่แม่นยำเกี่ยวกับความถี่เฟสและแอมพลิจูดสิ่งนี้ทำให้เป็นตัวเลือกที่ยอดเยี่ยมเมื่อคุณต้องการการสร้างสัญญาณที่ยืดหยุ่นและปรับได้ในระบบวิทยุหรืออุปกรณ์สื่อสารอื่น ๆ

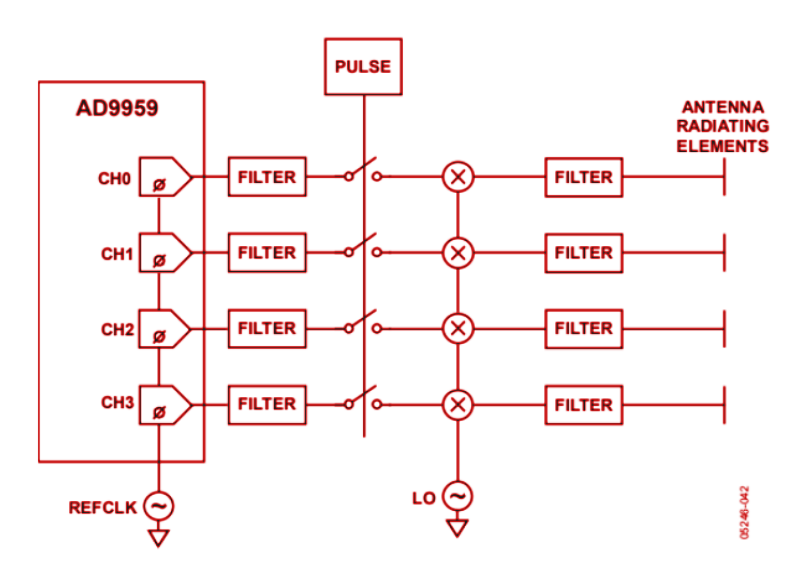

เรดาร์อาร์เรย์และโซนาร์

ในเรดาร์อาร์เรย์และระบบโซนาร์การซิงโครไนซ์ที่แม่นยำของช่องสัญญาณหลายช่องเป็นสิ่งสำคัญความสามารถของ AD9959 ในการจัดการการควบคุมและการซิงโครไนซ์ที่เป็นอิสระในหลายช่องทางทำให้เหมาะอย่างยิ่งสำหรับแอปพลิเคชันเหล่านี้ทำให้มั่นใจได้ว่าการประมวลผลสัญญาณและเวลาที่แม่นยำ

การใช้เครื่องมือ

AD9959 สามารถใช้ในเครื่องมือวัดประเภทต่าง ๆ โดยเฉพาะในอุปกรณ์ที่ต้องการการสร้างสัญญาณและการควบคุมที่แม่นยำไม่ว่าจะเป็นสำหรับการทดสอบการวัดหรือระบบสอบเทียบความยืดหยุ่นของอุปกรณ์ในการปรับความถี่เฟสและแอมพลิจูดจะเพิ่มความสามารถในการออกแบบของคุณ

การตอกย้ำแบบซิงโครไนซ์

สำหรับโครงการที่ต้องการการตอกบัตรที่ซิงโครไนซ์ในหลายช่องทาง AD9959 นำเสนอทางออกที่ยอดเยี่ยมคุณสมบัติการซิงโครไนซ์ในตัวช่วยให้คุณรักษาเวลาที่แน่นอนระหว่างช่องทางทำให้เหมาะสำหรับระบบที่ความแม่นยำของเวลามีความสำคัญ

แหล่งข้อมูล RF สำหรับตัวกรอง Acousto-Optic Tunable (AOTF)

AD9959 สามารถทำหน้าที่เป็นแหล่ง RF สำหรับตัวกรอง ACOUSTO-OPTIC ที่ปรับได้ (AOTF) ให้การสร้างสัญญาณที่เชื่อถือได้และแม่นยำสำหรับระบบออพติคอลเหล่านี้ความยืดหยุ่นในการควบคุมความถี่และแอมพลิจูดช่วยให้สามารถตอบสนองความต้องการของแอพพลิเคชั่นพิเศษดังกล่าว

AD9959 ภาพรวมวงจรแอปพลิเคชัน

Ad9959 ไดอะแกรมเค้าร่างมิติ

ข้อมูลผู้ผลิต AD9959

อุปกรณ์อะนาล็อกเป็น บริษัท ชั้นนำในการสร้างวงจรแบบบูรณาการตั้งแต่ปีพ. ศ. 2508 บริษัท มีความเชี่ยวชาญในการออกแบบและผลิตวงจรที่ช่วยแปลงสภาพและสัญญาณกระบวนการจากโลกแห่งความเป็นจริงเช่นอุณหภูมิเสียงและการเคลื่อนไหว - สัญญาณไฟฟ้าวงจรเหล่านี้ใช้ในระบบอิเล็กทรอนิกส์ที่หลากหลายทั่วโลก

คำถามที่พบบ่อย [คำถามที่พบบ่อย]

1. ใช้ AD9959 อะไร?

AD9959 มีแกนซินธิไซเซอร์ดิจิตอลโดยตรง (DDS) สี่แกนแต่ละตัวช่วยให้การควบคุมความถี่เฟสและแอมพลิจูดอย่างอิสระในช่องทางที่เกี่ยวข้องความยืดหยุ่นนี้สามารถช่วยให้คุณปรับสมดุลความไม่สอดคล้องใด ๆ ในสัญญาณที่เกิดจากกระบวนการอะนาล็อกเช่นการกรองการขยายหรือความแตกต่างของเค้าโครงบน PCB

2. AD9959 ทำงานอย่างไร?

AD9959 สามารถปรับความถี่เฟสหรือแอมพลิจูด (โดยใช้ FSK, PSK หรือถามการมอดูเลต) ด้วยระดับที่แตกต่างกันมากถึง 16 ระดับคุณควบคุมการมอดูเลตนี้โดยใช้สัญญาณกับพินโปรไฟล์ซึ่งช่วยให้ชิปสามารถสลับระหว่างระดับการมอดูเลตที่แตกต่างกันได้ตามต้องการ

เกี่ยวกับเรา

ALLELCO LIMITED

อ่านเพิ่มเติม

สอบถามรายละเอียดเพิ่มเติมอย่างรวดเร็ว

กรุณาส่งคำถามเราจะตอบกลับทันที

คู่มือที่ครอบคลุมเกี่ยวกับตัวแปลงแรงดันไฟฟ้า TC7660COA

บน 24/10/2024

ทำความเข้าใจ TIP120 ทรานซิสเตอร์

บน 24/10/2024

โพสต์ยอดนิยม

-

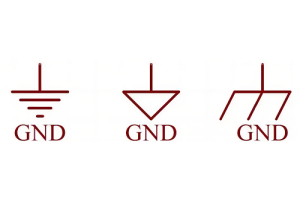

GND ในวงจรคืออะไร?

บน 01/01/1970 2925

-

คู่มือเชื่อมต่อ RJ-45: รหัสสีตัวเชื่อมต่อ RJ-45, แผนการเดินสาย, แอปพลิเคชัน R-J45, RJ-45 Datasheets

บน 01/01/1970 2484

-

ประเภทตัวเชื่อมต่อไฟเบอร์: SC vs LC และ LC กับ MTP

บน 01/01/1970 2075

-

การทำความเข้าใจแรงดันไฟฟ้าของแหล่งจ่ายไฟในอิเล็กทรอนิกส์ VCC, VDD, VEE, VSS และ GND

บน 08/11/0400 1864

-

การเปรียบเทียบระหว่าง DB9 และ RS232

บน 01/01/1970 1757

-

แบตเตอรี่ LR44 คืออะไร?

กระแสไฟฟ้าที่ใช้กำลังแพร่หลายแทรกซึมทุกแง่มุมของชีวิตประจำวันของเราตั้งแต่อุปกรณ์เล็กน้อยไปจนถึงอุปกรณ์การแพทย์ที่คุกคามชีวิตมันมีบทบาทเงียบอย่างไรก็ตามการเข้าใจพลังงานนี้อย่างแท้จริงโดยเฉพาะอย่างยิ่ง...บน 01/01/1970 1706

-

การทำความเข้าใจพื้นฐาน: การต่อต้านการเหนี่ยวนำและความสามารถพิเศษ

ในการเต้นรำที่ซับซ้อนของวิศวกรรมไฟฟ้าทั้งสามองค์ประกอบพื้นฐานต้องใช้เวทีกลาง: การเหนี่ยวนำความต้านทานและความจุแต่ละหมีมีลักษณะเฉพาะที่กำหนดจังหวะแบบไดนามิกของวงจรอิเล็กทรอนิกส์ที่นี่เราเริ่มต้นการเดินท...บน 01/01/1970 1649

-

คู่มือการใช้แบตเตอรี่ CR2430: ข้อมูลจำเพาะแอปพลิเคชันและการเปรียบเทียบกับแบตเตอรี่ CR2032

แบตเตอรี่ CR2430 คืออะไร?ประโยชน์ของแบตเตอรี่ CR2430บรรทัดฐานแอปพลิเคชันแบตเตอรี่ CR2430CR2430 เทียบเท่าCR2430 เทียบกับ CR2032ขนาดแบตเตอรี่ CR2430สิ่งที่จะมองหาเมื่อซื้อ CR2430 และเทียบเท่าแผ่นข้อมูล PDFคำถามที่พบบ่อย แบตเตอรี่เป็นห...บน 01/01/1970 1536

-

RF คืออะไรและทำไมเราถึงใช้มัน?

เทคโนโลยีความถี่วิทยุ (RF) เป็นส่วนสำคัญของการสื่อสารไร้สายที่ทันสมัยทำให้สามารถส่งข้อมูลในระยะทางไกลได้โดยไม่ต้องเชื่อมต่อทางกายภาพบทความนี้นำเสนอพื้นฐานของ RF อธิบายว่ารังสีแม่เหล็กไฟฟ้า (EMR) ทำให้การสื่อส...บน 01/01/1970 1528

-

CR2450 เทียบกับ CR2032: แบตเตอรี่สามารถใช้แทนได้หรือไม่?

แบตเตอรี่ลิเธียมแมงกานีสมีความคล้ายคลึงกับแบตเตอรี่ลิเธียมอื่น ๆความหนาแน่นของพลังงานสูงและอายุการใช้งานที่ยาวนานเป็นลักษณะที่พวกเขามีเหมือนกันแบตเตอรี่ชนิดนี้ได้รับความไว้วางใจและเป็นที่โปรดปรานของผู...บน 01/01/1970 1497