คู่มือนวัตกรรมสำหรับ JK Flip-Flops: การวิเคราะห์ตารางความจริงกลไกและแอพพลิเคชั่นเชิงกลยุทธ์

บทความนี้สำรวจสถาปัตยกรรมการดำเนินงานและแอพพลิเคชั่นที่หลากหลายของ JK Flip-Flop เริ่มต้นจากโครงสร้างพื้นฐานและความสัมพันธ์อินพุตเอาท์พุตผ่านกลไกการปฏิบัติงานโดยละเอียดไปจนถึงการใช้งานเชิงกลยุทธ์ในระบบดิจิตอลที่ซับซ้อนวาทกรรมขยายไปถึงการแยกความแตกต่างระหว่างตัวแปรที่ถูกกระตุ้นและทริกเกอร์ระดับการวิเคราะห์การวิเคราะห์ยูทิลิตี้ที่เกี่ยวข้องในสภาพแวดล้อมแบบซิงโครนัสและอะซิงโครนัสแคตตาล็อก

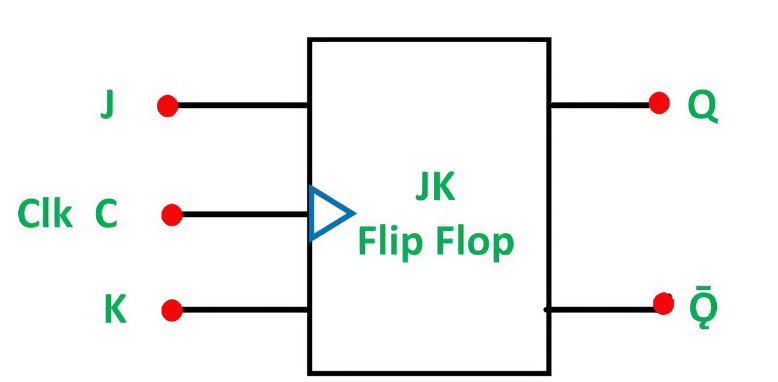

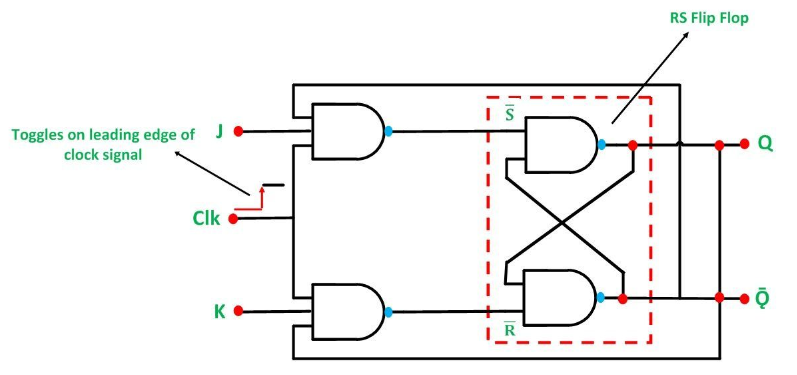

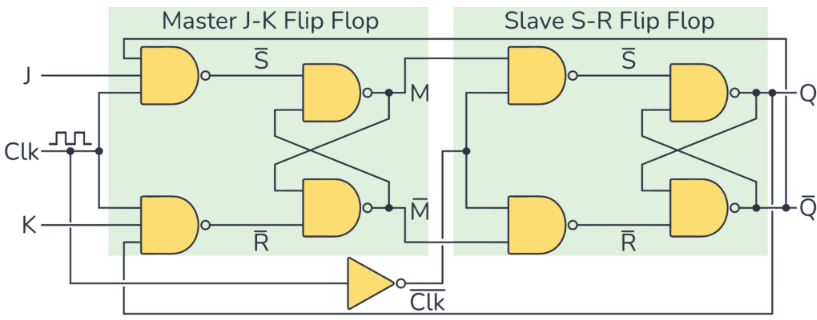

รูปที่ 1: JK Flip-Flop

พื้นฐานของ JK Flip-Flop

JK Flip-Flop เป็นองค์ประกอบพื้นฐานในอุปกรณ์อิเล็กทรอนิกส์ดิจิตอลที่ออกแบบมาเพื่อเก็บข้อมูลบิตเดียวมันสร้างขึ้นบน Flip-Flop SR ที่ง่ายขึ้นโดยการเพิ่มข้อเสนอแนะซึ่งช่วยป้องกันข้อผิดพลาดที่เรียกว่า "เงื่อนไขการแข่งขัน" ที่เอาต์พุตจะไม่เสถียร

Flip-Flop นี้มีอินพุตหลักสองตัวคือ J (Set) และ K (รีเซ็ต) และเอาต์พุตสองรายการ: Q และส่วนประกอบของมันคือ Q 'ผลลัพธ์เหล่านี้สะท้อนสถานะปัจจุบันอย่างต่อเนื่องและตรงกันข้ามทำให้วงจรสามารถปรับและตอบสนองต่อการเปลี่ยนแปลงอินพุตแบบเรียลไทม์

JK Flip-flop ทำงานในรูปแบบเฉพาะตามค่าอินพุต:

•เมื่อทั้ง J และ K เป็น 0: Flip-flop ถือสถานะปัจจุบันไม่มีการเปลี่ยนแปลงเกิดขึ้น

•เมื่อทั้ง J และ K คือ 1: ฟลิปฟล็อปสลับสถานะของมันถ้า Q คือ 0 มันจะกลายเป็น 1;หาก Q คือ 1 จะเปลี่ยนเป็น 0 การกระทำสลับนี้เป็นคุณสมบัติสำคัญที่แยกความแตกต่างของ JK Flip-Flop จากการออกแบบที่ง่ายกว่า

•เมื่อ j คือ 1 และ k คือ 0: Flip-flop ตั้งสถานะของมันทำให้ Q เท่ากับ 1

•เมื่อ j คือ 0 และ k คือ 1: Flip-flop รีเซ็ตทำให้ Q เท่ากับ 0

การทำงานของ JK Flip-Flop

JK Flip-Flop มีบทบาทสำคัญในวงจรดิจิตอลโดยการจัดการหน่วยความจำและเวลาผ่านการตอบสนองแบบประสานงานกับสัญญาณอินพุตและพัลส์นาฬิกาการทำงานของมันขึ้นอยู่กับช่วงเวลาของอินพุต J และ K ที่สัมพันธ์กับสัญญาณนาฬิกาซึ่งกำหนดว่าสถานะเอาต์พุต (Q และQ̅) เปลี่ยนไปอย่างไรการซิงโครไนซ์นี้ช่วยให้มั่นใจได้ว่า Flip-flop ทำงานได้อย่างคาดการณ์ได้ในการใช้งานวงจรต่างๆFlip-flop อาศัย NAND หรือหรือประตูเพื่อจัดการการเปลี่ยนแปลงของรัฐเหล่านี้

ถือสถานะปัจจุบัน- เมื่ออินพุตทั้ง J และ K ต่ำ (0) Flip-flop จะรักษาสถานะปัจจุบันประตูตรรกะอย่างมีประสิทธิภาพ "ล็อค" เอาต์พุตเพื่อให้มั่นใจว่าสถานะก่อนหน้า (สูงหรือต่ำ) จะได้รับการบำรุงรักษาฟังก์ชั่นการถือครองนี้มีความร้ายแรงในแอปพลิเคชันที่ข้อมูลจะต้องมีเสถียรภาพจนกว่าจะต้องมีการเปลี่ยนแปลงเฉพาะ

การตั้งค่าเอาต์พุตสูง (สถานะตั้ง) -เมื่อพัลส์นาฬิกาเกิดขึ้นและ J สูง (1) ในขณะที่ K ยังคงต่ำ (0) ประตูลอจิกปรับเพื่อตั้งค่าฟลิปฟล็อปสิ่งนี้ขับเคลื่อนเอาต์พุต Q ไปยังสถานะสูง (1)สิ่งนี้มีประโยชน์ในสถานการณ์ที่วงจรจำเป็นต้องเรียกใช้เอาต์พุตสูงเช่นการเปิดใช้งานอุปกรณ์หรือจัดเก็บ "1" ในหน่วยความจำ

การล้างเอาต์พุตต่ำ (รีเซ็ตสถานะ) - ถ้า j ต่ำ (0) และ k สูง (1) ในเวลาของการเต้นของนาฬิกาการเปลี่ยนฟลิปฟล็อปเป็นสถานะรีเซ็ตบังคับให้ Q ต้องต่ำ (0)การดำเนินการรีเซ็ตนี้มักจะใช้ในวงจรที่ต้องการสถานะเริ่มต้นหรือล้างหลังจากดำเนินการเสร็จสิ้นเช่นการล้างข้อมูลจากหน่วยความจำ

สลับเอาต์พุต - คุณสมบัติที่เป็นเอกลักษณ์ของ Flip-Flop ปรากฏขึ้นเมื่อทั้ง J และ K สูง (1)เมื่อพัลส์นาฬิกามาถึง Flip-flop สลับสลับเอาท์พุทจากสถานะปัจจุบันไปยังตรงกันข้ามถ้า Q สูงมันจะต่ำและถ้า Q ต่ำมันจะสูงฟังก์ชั่นสลับนี้ยืนยันในแอปพลิเคชันเช่นเคาน์เตอร์หรืออุปกรณ์ที่จำเป็นต้องสลับระหว่างรัฐโดยอัตโนมัติ

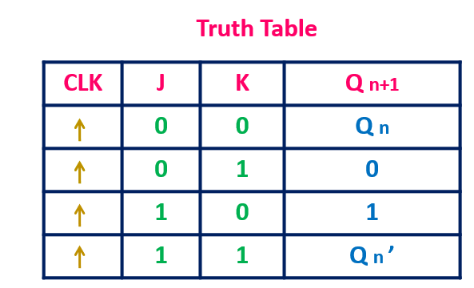

รูปที่ 2: ตารางความจริงของ JK Flip-Flop

การวิเคราะห์ตารางความจริงของ JK Flip-Flop

ตารางความจริงของ JK Flip-Flop เป็นเครื่องมือสำคัญสำหรับการแสดงให้เห็นว่ามันทำปฏิกิริยากับสัญญาณอินพุตที่แตกต่างกันในการซิงค์กับพัลส์นาฬิกาตารางนี้ช่วยในการออกแบบและแก้ไขปัญหาวงจรดิจิตอลโดยแสดงให้เห็นว่าเอาต์พุตของ Flip-Flop เปลี่ยนแปลงไปตามเงื่อนไขการป้อนข้อมูลที่หลากหลายอย่างไร

•ทั้ง J และ K ต่ำ (j = 0, k = 0): เมื่ออินพุตทั้งสองเป็น 0 Flip-Flop จะถือสถานะปัจจุบันไม่ว่า Q จะสูงหรือต่ำมันจะไม่เปลี่ยนแปลงนี่เป็นสิ่งสำคัญสำหรับวงจรที่ต้องการการเก็บข้อมูลที่เสถียรเช่นองค์ประกอบในหน่วยความจำซึ่งการรักษาสถานะปัจจุบันจะเหมาะสมจนกว่าจะมีการเปลี่ยนแปลงเฉพาะ

• j สูง, k ต่ำ (j = 1, k = 0): เมื่อ J คือ 1 และ K คือ 0 Flip-Flop จะตั้งค่าเอาต์พุต Q เป็นสูง (1)เงื่อนไขการตั้งค่านี้มีประโยชน์ในแอปพลิเคชันที่ต้องใช้ทริกเกอร์ที่แม่นยำในการเปิดใช้งานการดำเนินการเช่นการเปิดอุปกรณ์หรือเริ่มต้นลำดับในวงจรลอจิก

• j low, k สูง (j = 0, k = 1): ด้วย j ที่ 0 และ k ที่ 1 flip-flop จะรีเซ็ตทำให้ Q ต่ำ (0)ฟังก์ชั่นการรีเซ็ตนี้มีความร้ายแรงในระบบที่ต้องกลับสู่สถานะเริ่มต้นเช่นเมื่อล้างข้อมูลหรือเริ่มต้นกระบวนการ

•ทั้ง J และ K สูง (J = 1, K = 1): เมื่ออินพุตทั้งสองสูง Flip-flop จะสลับสถานะของมันถ้า Q สูงจะต่ำและถ้า Q ต่ำมันจะเปลี่ยนเป็นสูงพฤติกรรมการสลับแบบนี้เป็นสิ่งสำคัญสำหรับอุปกรณ์ที่จำเป็นต้องสลับกันระหว่างรัฐเช่นในตัวแบ่งความถี่หรือเคาน์เตอร์

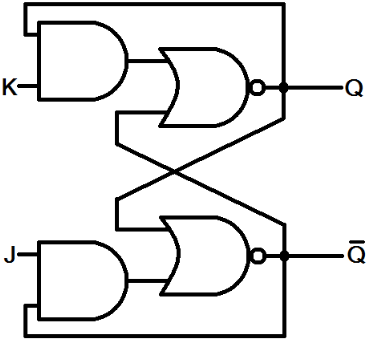

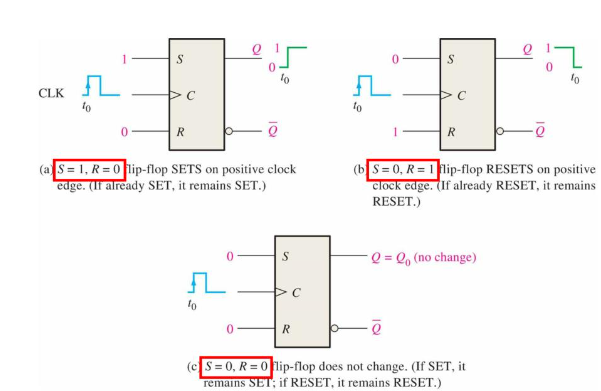

รูปที่ 3: JK latch

ข้อมูลเชิงลึกเกี่ยวกับการใช้งาน JK latch และการใช้งาน

JK latch ทำงานคล้ายกับ JK Flip-Flop แต่ไม่จำเป็นต้องมีสัญญาณนาฬิกาแทนที่จะรอขอบนาฬิกา JK latch ตอบสนองต่อการเปลี่ยนแปลงอย่างต่อเนื่องทำให้มันเป็น "ความไวต่อระดับ"ซึ่งหมายความว่าตราบใดที่อินพุต (J และ K) มีความเสถียรเอาต์พุตจะเปลี่ยนไปตามเวลาจริงโดยเสนอข้อเสนอแนะทันทีตามเงื่อนไขการป้อนข้อมูล

ซึ่งแตกต่างจาก JK Flip-Flop ที่ถูกกระตุ้นซึ่งอัพเดทเอาต์พุตเฉพาะเมื่อสัญญาณนาฬิกาเปลี่ยนไป (จากต่ำถึงสูงหรือในทางกลับกัน) JK latch จะปรับเอาต์พุตทันทีเมื่ออินพุตกะการตอบสนองแบบเรียลไทม์คงที่นี้มีค่าในสถานการณ์ที่ต้องการการกระทำทันทีโดยไม่ล่าช้าที่เกิดจากการซิงโครไนซ์นาฬิกา

ตัวกรองเสียงรบกวน: ในวงจรดิจิตอลที่ต้องกรองเสียงรบกวนที่ไม่พึงประสงค์อย่างรวดเร็วปฏิกิริยาตอบสนองทันทีของ JK Latch ต่อการเปลี่ยนแปลงอินพุตนั้นมีอิทธิพลเนื่องจากไม่รอการเต้นของนาฬิกามันสามารถปรับเอาท์พุทได้ทันทีที่ตรวจพบเสียงรบกวนทำให้เกิดความล่าช้าในการแก้ไขสัญญาณ

องค์ประกอบหน่วยความจำอย่างง่าย: สลัก JK สามารถทำหน้าที่เป็นหน่วยหน่วยความจำพื้นฐานในระบบที่ไม่ต้องการการควบคุมที่ซับซ้อนเนื่องจากสลักช่วยให้เอาต์พุตเสถียรตราบใดที่อินพุตไม่เปลี่ยนแปลงจึงถือสถานะปัจจุบันได้อย่างมีประสิทธิภาพซึ่งมีประโยชน์สำหรับวงจรที่จำเป็นต้องเก็บข้อมูลโดยไม่ต้องมีค่าใช้จ่ายในการดำเนินการ

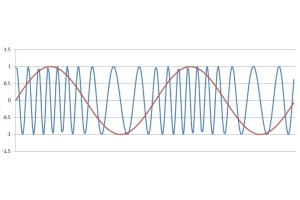

รูปที่ 4: การวิเคราะห์แผนภาพเวลาสำหรับ JK Flip-Flop

การวิเคราะห์แผนภาพเวลาของ JK Flip-Flops

ไดอะแกรมเวลาของ JK Flip-Flop ให้การแยกแยะภาพว่าเอาต์พุตตอบสนองต่ออินพุตที่แตกต่างกันซึ่งซิงโครไนซ์กับการเปลี่ยนพัลส์ของนาฬิกาแผนภาพนี้แสดงความสัมพันธ์ระหว่างสัญญาณนาฬิกา (CLK) และอินพุต (j และ k) และวิธีที่พวกเขามีอิทธิพลต่อเอาต์พุต (Q และ Q ')ช่วยในการแมปพฤติกรรมของ Flip-Flop ในรัฐต่อเนื่องทำให้เข้าใจได้ง่ายขึ้น

ประการแรกแผนภาพ ไฮไลต์ว่าเอาต์พุตจะได้รับการอัปเดตเฉพาะบนขอบที่เพิ่มขึ้นหรือลดลงของพัลส์นาฬิกา-คุณลักษณะนี้เรียกว่าการกระตุ้นขอบนั้นโดดเด่นในการดำเนินการของ JK Flip-Flopมันแสดงให้เห็นว่าแม้ว่าอินพุต j และ k จะเปลี่ยนแปลงเอาต์พุตยังคงไม่เปลี่ยนแปลงจนกว่าขอบนาฬิกาจะเกิดขึ้น

จากนั้นเมื่อไดอะแกรมแมปการเปลี่ยนแปลงของอินพุต j และ k มันก็มองเห็นได้ แสดงให้เห็นว่าการรวมอินพุตแต่ละครั้งมีผลต่อเอาต์พุตอย่างไร ตัวอย่างเช่นเมื่อทั้ง J และ K ต่ำ (0) เอาท์พุทจะถือสถานะปัจจุบันเมื่อ j สูงและ k ต่ำจะมีการตั้งค่าเอาต์พุตการแสดงภาพที่ชัดเจนนี้ช่วยให้ผู้ใช้เข้าใจว่า Flip-flop ตอบสนองต่อการรวมอินพุตที่แตกต่างกันในแบบเรียลไทม์ได้อย่างไร

ในที่สุด, แผนภาพเวลาแสดงการเปลี่ยนแปลงระหว่างสถานะเอาท์พุทที่แตกต่างกันอย่างชัดเจนไม่ว่าจะเป็นการถือการตั้งค่ารีเซ็ตหรือสลับ-การเปลี่ยนแปลงของแต่ละรัฐจะเชื่อมโยงโดยตรงกับเงื่อนไขการป้อนข้อมูลและขอบนาฬิกาแสดงความสัมพันธ์ระหว่างสาเหตุและผลกระทบที่โฟกัสสำหรับการออกแบบและการแก้ไขปัญหาวงจร

แอพพลิเคชั่นอเนกประสงค์ของ JK Flip-Flops

JK Flip-Flop เป็นส่วนประกอบหลักในระบบดิจิตอลที่หลากหลายซึ่งเป็นที่รู้จักกันดีในเรื่องความยืดหยุ่นและความน่าเชื่อถือความสามารถในการจัดการการดำเนินการตรรกะที่ซับซ้อนทำให้พวกเขาจำเป็นในแอปพลิเคชันหลักหลายอย่างรวมถึง:

รูปที่ 5: ที่เก็บหน่วยความจำ

JK flip-flop มักใช้เพื่อเก็บข้อมูลแต่ละบิตของข้อมูลทำให้องค์ประกอบพื้นฐานในอาร์เรย์หน่วยความจำและการลงทะเบียนFlip-flop แต่ละตัวถือหนึ่งบิตทำให้มั่นใจได้ว่าการจัดเก็บข้อมูลที่เชื่อถือได้ซึ่งเป็นประโยชน์ในการออกแบบระบบหน่วยความจำขนาดใหญ่

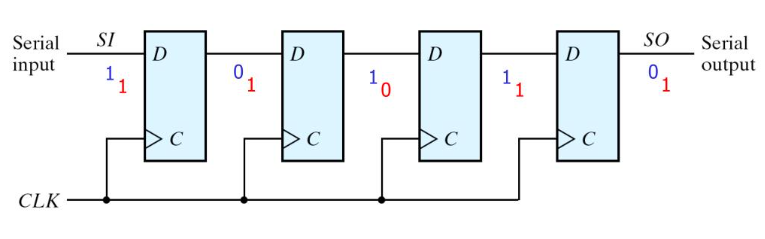

รูปที่ 6: เคาน์เตอร์และการลงทะเบียนกะ

JK Flip-Flop เป็นแบบไดนามิกในการดำเนินการตามลำดับพวกเขาจะใช้กันอย่างแพร่หลายในเคาน์เตอร์สำหรับการนับเหตุการณ์หรือพัลส์และในการลงทะเบียน Shift สำหรับการแปลงข้อมูลอนุกรมเป็นรูปแบบขนานสิ่งนี้ทำให้พวกเขามีประโยชน์ในการจัดการและจัดการข้อมูลในขั้นตอนต่าง ๆ ของกระบวนการเช่นในระบบการสื่อสาร

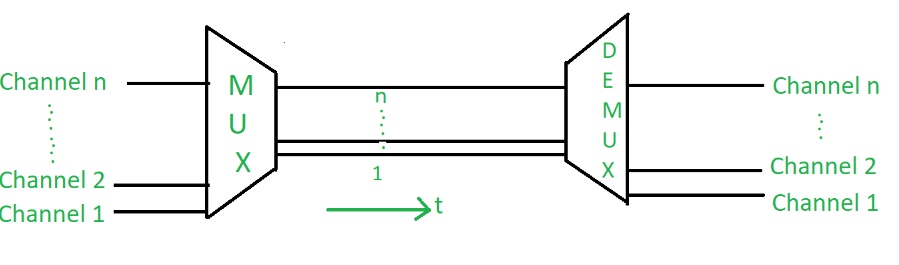

รูปที่ 7: การแบ่งความถี่

ในการประมวลผลสัญญาณ JK flip-flop มักจะใช้สำหรับการแบ่งความถี่โดยการสลับสถานะของพวกเขาด้วยชีพจรนาฬิกาแต่ละตัวพวกเขาจะแบ่งความถี่ของสัญญาณอินพุตสร้างสัญญาณนาฬิกาที่ช้ากว่าและจัดการได้มากขึ้นนี่เป็นสิ่งสำคัญในแอปพลิเคชันเช่นการจัดการสัญญาณนาฬิกาซึ่งต้องการการควบคุมเวลา

รูปที่ 8: การซิงโครไนซ์

JK Flip-Flops ช่วยซิงโครไนซ์หลายกระบวนการดิจิตอลโดยทำให้มั่นใจว่าส่วนต่าง ๆ ของระบบทำงานร่วมกันในลักษณะที่ประสานงานกันพวกเขามั่นใจว่าส่วนประกอบต่าง ๆ ตอบสนองอย่างถูกต้องกับสัญญาณที่กำหนดเวลาทำให้ระบบทั้งหมดอยู่ในการซิงค์

รูปที่ 9: JK Flip-Flop: Edge-Triggered และ Triggered

jk flip-flops ประเภทต่าง ๆ

JK Flip-Flops มีให้เลือกสองประเภทหลัก: การเรียกใช้ขอบและทริกเกอร์ระดับแต่ละแบบออกแบบตามข้อกำหนดการปฏิบัติงานที่แตกต่างกัน

JK Flip-Flops ที่ถูกกระตุ้นด้วยขอบ: เปลี่ยนสถานะของพวกเขาเฉพาะที่จุดเฉพาะ - เมื่อสัญญาณนาฬิกาเปลี่ยนจากต่ำถึงสูง (ขอบสูง) หรือสูงถึงต่ำ (ขอบที่ตกลงมา)ลักษณะนี้ทำให้พวกเขาเหมาะสำหรับระบบที่เวลาที่แม่นยำยืนหยัดเนื่องจากการเปลี่ยนแปลงของรัฐเกิดขึ้นที่ขอบนาฬิกา flip-flop เหล่านี้ทำให้แน่ใจว่าการอัปเดตทั้งหมดเกิดขึ้นในการซิงค์กับพัลส์นาฬิกาพฤติกรรมที่คาดการณ์ได้นี้เป็นแบบไดนามิกในสภาพแวดล้อมที่มีการควบคุมอย่างเข้มงวดเช่นนาฬิกาดิจิตอลการลงทะเบียนและวงจรต่อเนื่องส่วนใหญ่ที่นี่ระยะเวลาของการเปลี่ยนแปลงแต่ละครั้งนั้นร้ายแรงต่อการรักษาเสถียรภาพของระบบและทำให้มั่นใจว่าการดำเนินการจะถูกซิงโครไนซ์

jk flip-flops ที่ถูกกระตุ้นระดับ: ทำงานที่แตกต่างกันตอบสนองต่อสัญญาณอินพุตตราบใดที่สัญญาณนาฬิกาอยู่ในระดับใดระดับหนึ่งไม่ว่าจะสูงหรือต่ำพวกเขาไม่รอการเปลี่ยนแปลงนาฬิกาที่เฉพาะเจาะจงแต่ตราบใดที่อินพุตเป็นไปตามเงื่อนไขที่ต้องการ Flip-flop จะเปลี่ยนสถานะพฤติกรรมนี้ทำให้ Flip-Flop ที่ถูกกระตุ้นระดับดีขึ้นเหมาะกับระบบอะซิงโครนัสซึ่งอินพุตอาจไม่สอดคล้องกับพัลส์นาฬิกาปกติพวกเขาให้ความยืดหยุ่นในระบบที่อินพุตไม่สามารถคาดเดาได้หรือมาถึงช่วงเวลาที่ผิดปกติเช่นในงานการประมวลผลสัญญาณหรือระบบการตรวจสอบที่ต้องตอบสนองต่อการเปลี่ยนอินพุตทันที

ข้อดีและข้อเสียของ JK Flip-Flop

JK Flip-Flops มีประโยชน์หลายประการ แต่ยังมาพร้อมกับการแลกเปลี่ยนบางอย่างที่ต้องชั่งน้ำหนักอย่างรอบคอบเมื่อออกแบบระบบดิจิตอล

|

ผู้เชี่ยวชาญ |

|

|

ความอเนกประสงค์ |

jk flip-flop มีความยืดหยุ่นสูงและสามารถทำได้

ใช้ในวงจรดิจิตอลต่างๆเช่นที่เก็บหน่วยความจำเคาน์เตอร์และ

ระบบควบคุมพวกเขาสามารถสลับตั้งค่าหรือรีเซ็ตตามอินพุตที่แตกต่างกัน

เงื่อนไขทำให้เหมาะสำหรับการใช้งานที่หลากหลาย

ต้องการการควบคุมที่แม่นยำในการเปลี่ยนสถานะ |

|

กลไกการแก้ไขตนเอง |

หนึ่งในคุณสมบัติที่โดดเด่นของ JK

Flip-Flop เป็นลูปตอบรับในตัวของพวกเขาซึ่งช่วยแก้ไขเหตุผลเชิงตรรกะ

รัฐแบบไดนามิกการแก้ไขตนเองนี้ทำให้มั่นใจได้ว่าวงจรยังคงอยู่

เสถียรในระหว่างการทำงานแม้ว่าอินพุตจะเปลี่ยนแปลงอย่างรวดเร็ว |

|

การลดสภาพการแข่งขัน |

JK Flip-Flops ซึ่งแตกต่างจากรองเท้าแตะที่เรียบง่าย JK Flip-Flops

ได้รับการออกแบบมาเพื่อป้องกันสภาพการแข่งขัน - การตัดสินที่เอาท์พุทจะกลายเป็น

ไม่เสถียรเนื่องจากสัญญาณอินพุตที่ขัดแย้งกันความสามารถในการบำรุงรักษานี้

เอาต์พุตที่สอดคล้องกันแม้ภายใต้การเปลี่ยนแปลงอินพุตที่รวดเร็วและต่อเนื่องปรับปรุง

ความน่าเชื่อถือของวงจร |

|

ข้อเสีย |

|

|

การออกแบบที่ซับซ้อน |

jk flip-flop มีความซับซ้อนมากกว่า

รองเท้าแตะพื้นฐานการออกแบบของพวกเขาต้องการประตูตรรกะและอินพุตเพิ่มเติม

การตรวจสอบซึ่งสามารถทำให้วงจรยากขึ้นในการออกแบบและ

แก้ไขปัญหาโดยเฉพาะอย่างยิ่งในระบบที่ต้องการความเรียบง่าย |

|

ความล่าช้าในการขยายพันธุ์ |

gating ภายในที่ใช้ในการจัดการสถานะ

การเปลี่ยนแปลงแนะนำความล่าช้าในการประมวลผลสัญญาณที่รวดเร็วใน

แอพพลิเคชั่นความเร็วสูงความล่าช้านี้อาจส่งผลกระทบต่อเวลาโดยรวมและช้าลง

ประสิทธิภาพของวงจร |

|

การใช้พลังงานที่สูงขึ้น |

เนื่องจากความซับซ้อนและความต้องการ

ตรวจสอบเงื่อนไขการป้อนข้อมูลอย่างต่อเนื่อง JK Flip-Flops ใช้พลังงานมากขึ้น

เมื่อเทียบกับรองเท้าแตะที่ง่ายกว่าในระบบขนาดใหญ่หรือไวต่อพลังงาน

แอปพลิเคชันความต้องการพลังงานที่สูงขึ้นนี้อาจกลายเป็นข้อเสียเปรียบ |

รูปที่ 10: Master-Slave JK Flip-Flop

การถอดรหัส JK Flip-Flop หลัก

Master-Slave JK Flip-Flop ได้รับการออกแบบมาเพื่อแก้ปัญหาสภาพการแข่งขันที่พบใน Flip-Flop JK มาตรฐานโดยใช้กระบวนการสองขั้นตอนเพื่อจัดการอินพุตและเอาต์พุตได้อย่างมีประสิทธิภาพมากขึ้น

ขั้นตอนแรกที่เรียกว่าเวทีหลักจะจับค่าอินพุตเมื่อสัญญาณนาฬิกาถึงขอบเฉพาะไม่ว่าจะเพิ่มขึ้นหรือลดลงณ จุดนี้ข้อมูลอินพุตจะถูกล็อคซึ่งหมายความว่าการเปลี่ยนแปลงเพิ่มเติมของอินพุตจะไม่ส่งผลกระทบต่อสถานะที่จับได้จนกว่าจะถึงรอบนาฬิกาถัดไปขั้นตอนนี้ทำให้มั่นใจได้ว่า Flip-Flop จะลงทะเบียนอินพุตที่ถูกต้องโดยไม่ได้รับอิทธิพลจากการเปลี่ยนแปลงใด ๆ ที่ตามมาในระหว่างรอบนาฬิกาเดียวกัน

หลังจากเวทีหลักเสร็จสิ้นเวทีทาสจะเข้ามาเล่นขั้นตอนนี้จะอัปเดตเอาต์พุตตามข้อมูลที่บันทึกโดยเวทีหลัก แต่เฉพาะที่ขอบนาฬิกาถัดไปโดยการแยกการจับอินพุตออกจากการอัปเดตเอาต์พุตระยะทาสทำให้มั่นใจได้ว่าเอาต์พุตจะยังคงมีความเสถียรจนกว่าระยะหลักจะประมวลผลอินพุตอย่างสมบูรณ์สิ่งนี้จะช่วยป้องกันการเปลี่ยนแปลงก่อนกำหนดหรือไม่ได้ตั้งใจในเอาต์พุตในระหว่างรอบนาฬิกา

เหตุใดการกำหนดค่าหลัก-ทาสจึงมีความสำคัญ?

กระบวนการสองขั้นตอนทำให้การทำงานของ JK flip-flop มีความเสถียรป้องกันการแกว่งหรือความผันผวนที่ไม่พึงประสงค์ที่สามารถเกิดขึ้นได้ในการกำหนดค่าที่ง่ายขึ้นโดยเฉพาะอย่างยิ่งเมื่ออินพุตทั้งสองอยู่สูงโดยการแยกการประมวลผลอินพุตจากการเปลี่ยนแปลงเอาต์พุตการกำหนดค่าหลักทาสทำให้มั่นใจได้ว่าเอาต์พุตยังคงคาดเดาได้และเสถียรแม้ในสถานการณ์ที่เวลามีค่า

พูดถึงการแข่งขันรอบ ๆ สภาพใน JK Flip-Flops

เงื่อนไขการแข่งขันรอบเกิดขึ้นใน jk flip-flop เมื่อทั้งอินพุต, J และ K สูงและสัญญาณนาฬิกายังคงทำงานอยู่นานเกินไปสิ่งนี้นำไปสู่การสลับเอาต์พุตอย่างต่อเนื่องซึ่งอาจทำให้เกิดพฤติกรรมที่ไม่แน่นอนและขัดขวางความน่าเชื่อถือของวงจร

การตั้งค่า Master-Slave ใช้กระบวนการสองขั้นตอนเพื่อป้องกันปัญหาการแข่งขันรอบเวทีหลักจะจับค่าอินพุตที่ขอบนาฬิกาและล็อคไว้ในเวทีทาสจะอัปเดตเอาต์พุตที่ขอบนาฬิกาถัดไปเพื่อให้แน่ใจว่าเอาต์พุตจะไม่เปลี่ยนแปลงจนกว่าอินพุตจะถูกประมวลผลอย่างสมบูรณ์วิธีการนี้ช่วยป้องกันเอาท์พุทจากการสลับอย่างไม่สามารถควบคุมได้แม้ว่าอินพุตจะยังคงสูงเป็นระยะเวลานาน

อีกวิธีหนึ่งในการหลีกเลี่ยงเงื่อนไขการแข่งขันคือการปรับระยะเวลาการเต้นของนาฬิกาด้วยการทำให้นาฬิกาพัลส์สั้นกว่าความล่าช้าในการแพร่กระจายของ Flip-Flop คุณสามารถมั่นใจได้ว่าสถานะจะไม่เปลี่ยนแปลงมากกว่าหนึ่งครั้งภายในรอบนาฬิกาเดียวกันสิ่งนี้จะช่วยป้องกันไม่ให้ Flip-Flop สลับซ้ำ ๆ ในระหว่างรอบเดียวทำให้เสถียรของเอาต์พุต

พลวัตของการสลับใน jk flip-flops

พฤติกรรมการสลับของ JK Flip-Flop นั้นส่วนใหญ่ขับเคลื่อนด้วยเวลาของสัญญาณนาฬิกาและระดับอินพุต (J และ K)Flip-flop เปลี่ยนสถานะตามอินพุตที่มีอยู่ที่ขอบบวกของสัญญาณนาฬิกาในช่วงเวลาที่อันตรายนี้ Flip-Flop จะประเมินอินพุตและอัปเดตเอาต์พุตตามลำดับ

เมื่อสัญญาณนาฬิกากระทบกับขอบที่เพิ่มขึ้น JK Flip-Flop จะอ่านสถานะปัจจุบันของอินพุต J และ Kขึ้นอยู่กับค่าของพวกเขา flip-flop จะถือตั้งค่ารีเซ็ตหรือสลับเอาต์พุต

นาฬิกาดิจิตอล: ความแม่นยำคือทุกอย่างในนาฬิกาดิจิตอลและ JK Flip-Flops ช่วยรักษาความแม่นยำนี้โดยการทำให้มั่นใจว่าการเปลี่ยนแปลงของสถานะเกิดขึ้นในช่วงเวลานาฬิกาที่แม่นยำเท่านั้น

ผู้ทดสอบตรรกะตามลำดับ: ในระบบที่ทดสอบการทำงานของวงจรลอจิก JK Flip-Flops มีบทบาทในการตรวจสอบว่าแต่ละองค์ประกอบตอบสนองอย่างถูกต้องกับสัญญาณที่กำหนดเวลาเฉพาะ

ระบบที่ไวต่อเวลาอื่น ๆ : ในแอพพลิเคชั่นดิจิตอลต่างๆที่มีความเสี่ยงเช่นระบบการสื่อสารหรือหน่วยประมวลผลข้อมูล JK Flip-Flop ทำให้มั่นใจได้ว่าการเปลี่ยนแปลงของรัฐเกิดขึ้นในการซิงค์กับนาฬิกาเพื่อป้องกันข้อผิดพลาดของเวลา

บทสรุป

JK Flip-Flop โดดเด่นเป็นองค์ประกอบที่ดีที่สุดในการออกแบบวงจรดิจิตอลนำเสนอการผสมผสานของความเก่งกาจและความแม่นยำที่สิ้นหวังสำหรับแอพพลิเคชั่นที่หลากหลายตั้งแต่การจัดเก็บหน่วยความจำไปจนถึงการแบ่งความถี่และการซิงโครไนซ์ของกระบวนการดิจิตอลความสามารถในการลดสภาพการแข่งขันผ่านการกำหนดค่าที่เป็นนวัตกรรมเช่นการจัดเรียงหลัก-สลาวด์ตอกย้ำความสามารถในการปรับตัวในการแก้ไขความท้าทายในการออกแบบโดยธรรมชาติบทบาทหลุมฝังศพของ Flip-Flop อย่างเท่าเทียมกันในการสร้างความมั่นใจว่าการเปลี่ยนแปลงของรัฐที่แม่นยำเน้นถึงลักษณะที่จำเป็นในการสร้างและบำรุงรักษาระบบดิจิตอลที่เชื่อถือได้และมีประสิทธิภาพเมื่อเทคโนโลยีก้าวหน้าไปการออกแบบและการประยุกต์ใช้การพัฒนาของ JK Flip-Flop ยังคงเป็นกุญแจสำคัญในการผลักดันขอบเขตของอุปกรณ์อิเล็กทรอนิกส์ดิจิตอลไปสู่สถาปัตยกรรมที่ซับซ้อนและแข็งแกร่งยิ่งขึ้น

คำถามที่พบบ่อย [คำถามที่พบบ่อย]

1. แอพพลิเคชั่นของ JK Flip Flop คืออะไร?

JK Flip-Flop ใช้อย่างกว้างขวางในอุปกรณ์อิเล็กทรอนิกส์ดิจิตอลสำหรับงานที่หลากหลาย:

แอปพลิเคชันเวลา: มันสามารถทำหน้าที่เป็นองค์ประกอบความล่าช้าหรือตัวจับเวลาเมื่อเชื่อมต่อในการกำหนดค่าบางอย่าง

เคาน์เตอร์และทะเบียน: ด้วยการสลับสถานะด้วยชีพจรนาฬิกาแต่ละครั้งมันจะใช้ในการออกแบบเคาน์เตอร์และการลงทะเบียนกะที่หลากหลายซึ่งเป็นสุดยอดในวงจรตรรกะตามลำดับ

ที่เก็บหน่วยความจำ: มันมีหน่วยพื้นฐานของการจัดเก็บหน่วยความจำซึ่งมีประโยชน์ในการจัดเก็บบิตในแอปพลิเคชันการคำนวณ

2. JK flip-flop ทำงานกับตารางความจริงได้อย่างไร?

JK Flip-Flop มีอินพุตสองอินพุต (J และ K) และสัญญาณนาฬิกาการทำงานของมันแตกต่างกันไปตามสถานะอินพุตซิงโครไนซ์กับนาฬิกา:

• j = 0, k = 0: เอาต์พุตไม่เปลี่ยนแปลง

• j = 0, k = 1: เอาต์พุตรีเซ็ตเป็น 0

• j = 1, k = 0: เอาต์พุตถูกตั้งค่าเป็น 1

• j = 1, k = 1: การสลับเอาต์พุต (เช่นถ้าเป็น 0 มันจะกลายเป็น 1 และในทางกลับกัน)

3. JK Flip Flop คืออะไรและใช้งานได้หรือไม่?

JK flip-flop รวมคุณสมบัติของรองเท้าแตะ SR และ Tมันหลีกเลี่ยงเงื่อนไข "ต้องห้าม" ที่เห็นใน SR Flip-Flops โดยใช้อินพุต JK ได้อย่างมีประสิทธิภาพ:

สถานะของ flip-flop ถูกควบคุมโดยอินพุต j และ k ซึ่งเป็นตัวกำหนดว่าเอาต์พุตควรเก็บรีเซ็ตตั้งค่าหรือสลับเพื่อซิงค์กับขอบที่เพิ่มขึ้นหรือลดลงของชีพจรนาฬิกา

4. แอพพลิเคชั่นของสลักและรองเท้าแตะคืออะไร?

การจัดเก็บข้อมูล: สลักและรองเท้าแตะเป็นเรื่องจริงจังสำหรับการจัดเก็บข้อมูลภายในการลงทะเบียนและอาร์เรย์หน่วยความจำ

การแบ่งความถี่: ใช้ในตัวแบ่งความถี่เนื่องจากความสามารถในการเปลี่ยนสถานะบนขอบนาฬิกาลดความถี่ลงครึ่งหนึ่งในแต่ละขั้นตอนในซีรีส์

เครื่องจักรของรัฐ: พื้นฐานในการออกแบบเครื่องสถานะ จำกัด ซึ่งใช้ในการใช้งานตามลำดับตรรกะและวงจรควบคุม

debouncing: ใช้ในการทำให้สัญญาณเสถียรจากสวิตช์และปุ่มเชิงกลทำให้มั่นใจได้ว่าการเปลี่ยนผ่านแบบเดียวและสะอาด

5. รองเท้าแตะใช้ทำอะไร?

ที่เก็บไบนารี: Flip-flop แต่ละตัวเก็บข้อมูลหนึ่งบิตทำให้พวกเขาสร้างบล็อกสำหรับอุปกรณ์จัดเก็บข้อมูลไบนารี

ตัวแบ่งนาฬิกา: พวกเขาแบ่งความถี่นาฬิกาอินพุตเป็นสองอย่างมีประโยชน์ในนาฬิกาดิจิตอลและแอปพลิเคชันเวลา

เกี่ยวกับเรา

ALLELCO LIMITED

อ่านเพิ่มเติม

สอบถามรายละเอียดเพิ่มเติมอย่างรวดเร็ว

กรุณาส่งคำถามเราจะตอบกลับทันที

JRC4558 OP-AMP: คุณสมบัติข้อมูลจำเพาะและแอปพลิเคชัน

บน 18/09/2024

ตัวต้านทาน 330 โอห์มและรหัสสี

บน 13/09/2024

โพสต์ยอดนิยม

-

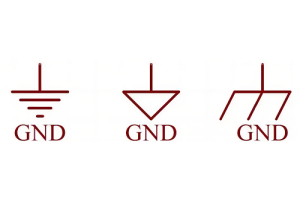

GND ในวงจรคืออะไร?

บน 01/01/1970 2946

-

คู่มือเชื่อมต่อ RJ-45: รหัสสีตัวเชื่อมต่อ RJ-45, แผนการเดินสาย, แอปพลิเคชัน R-J45, RJ-45 Datasheets

บน 01/01/1970 2502

-

ประเภทตัวเชื่อมต่อไฟเบอร์: SC vs LC และ LC กับ MTP

บน 01/01/1970 2091

-

การทำความเข้าใจแรงดันไฟฟ้าของแหล่งจ่ายไฟในอิเล็กทรอนิกส์ VCC, VDD, VEE, VSS และ GND

บน 09/11/0400 1898

-

การเปรียบเทียบระหว่าง DB9 และ RS232

บน 01/01/1970 1765

-

แบตเตอรี่ LR44 คืออะไร?

กระแสไฟฟ้าที่ใช้กำลังแพร่หลายแทรกซึมทุกแง่มุมของชีวิตประจำวันของเราตั้งแต่อุปกรณ์เล็กน้อยไปจนถึงอุปกรณ์การแพทย์ที่คุกคามชีวิตมันมีบทบาทเงียบอย่างไรก็ตามการเข้าใจพลังงานนี้อย่างแท้จริงโดยเฉพาะอย่างยิ่ง...บน 01/01/1970 1714

-

การทำความเข้าใจพื้นฐาน: การต่อต้านการเหนี่ยวนำและความสามารถพิเศษ

ในการเต้นรำที่ซับซ้อนของวิศวกรรมไฟฟ้าทั้งสามองค์ประกอบพื้นฐานต้องใช้เวทีกลาง: การเหนี่ยวนำความต้านทานและความจุแต่ละหมีมีลักษณะเฉพาะที่กำหนดจังหวะแบบไดนามิกของวงจรอิเล็กทรอนิกส์ที่นี่เราเริ่มต้นการเดินท...บน 01/01/1970 1662

-

คู่มือการใช้แบตเตอรี่ CR2430: ข้อมูลจำเพาะแอปพลิเคชันและการเปรียบเทียบกับแบตเตอรี่ CR2032

แบตเตอรี่ CR2430 คืออะไร?ประโยชน์ของแบตเตอรี่ CR2430บรรทัดฐานแอปพลิเคชันแบตเตอรี่ CR2430CR2430 เทียบเท่าCR2430 เทียบกับ CR2032ขนาดแบตเตอรี่ CR2430สิ่งที่จะมองหาเมื่อซื้อ CR2430 และเทียบเท่าแผ่นข้อมูล PDFคำถามที่พบบ่อย แบตเตอรี่เป็นห...บน 01/01/1970 1567

-

RF คืออะไรและทำไมเราถึงใช้มัน?

เทคโนโลยีความถี่วิทยุ (RF) เป็นส่วนสำคัญของการสื่อสารไร้สายที่ทันสมัยทำให้สามารถส่งข้อมูลในระยะทางไกลได้โดยไม่ต้องเชื่อมต่อทางกายภาพบทความนี้นำเสนอพื้นฐานของ RF อธิบายว่ารังสีแม่เหล็กไฟฟ้า (EMR) ทำให้การสื่อส...บน 01/01/1970 1550

-

CR2450 เทียบกับ CR2032: แบตเตอรี่สามารถใช้แทนได้หรือไม่?

แบตเตอรี่ลิเธียมแมงกานีสมีความคล้ายคลึงกับแบตเตอรี่ลิเธียมอื่น ๆความหนาแน่นของพลังงานสูงและอายุการใช้งานที่ยาวนานเป็นลักษณะที่พวกเขามีเหมือนกันแบตเตอรี่ชนิดนี้ได้รับความไว้วางใจและเป็นที่โปรดปรานของผู...บน 01/01/1970 1519