การเรียนรู้ SR latches: สัญลักษณ์ฟังก์ชั่นและแอปพลิเคชันที่ใช้งานได้จริง

สลัก SR เป็นวงจรแบบอะซิงโครนัสที่ทำงานอย่างอิสระจากสัญญาณนาฬิกาทำให้เป็นเครื่องมือที่หลากหลายในแอปพลิเคชันต่างๆมันรักษาสถานะไบนารี - ไม่ว่าจะสูง (1) หรือต่ำ (0) - และสามารถเก็บข้อมูลบิตเดียวซึ่งถือได้จนกว่าสัญญาณอินพุตใหม่จะกำหนดการเปลี่ยนแปลงองค์ประกอบการจัดเก็บข้อมูลไบนารีพื้นฐานนี้ถูกสร้างขึ้นโดยใช้ประตูตรรกะข้ามคู่สองประตูโดยทั่วไปหรือประตู NAND หรือ NANDการตั้งค่าอินพุต (S) เปิดใช้งานสลักตั้งค่าเอาต์พุต (q) เป็นสูงในขณะที่อินพุตรีเซ็ต (R) ตั้งค่าเอาต์พุตเป็นต่ำอย่างไรก็ตามสัญญาณสูงพร้อมกันของอินพุตทั้งสองนำไปสู่สถานะที่ไม่ได้กำหนดนักออกแบบเงื่อนไขจะต้องหลีกเลี่ยงสลัก SR ไม่ได้เป็นเพียงแค่โครงสร้างทางทฤษฎีเท่านั้นพวกเขาจะถูกนำไปใช้ในระบบปฏิบัติเพื่อเก็บข้อมูลชั่วคราวสนับสนุนผลการประมวลผลระดับกลางและแม้แต่จัดการการตรวจจับข้อผิดพลาดในแอพพลิเคชั่นที่สำคัญเช่นการบินและอวกาศและอุปกรณ์การแพทย์แสดงให้เห็นถึงความขาดแคลนในการออกแบบวงจรดิจิตอลแคตตาล็อก

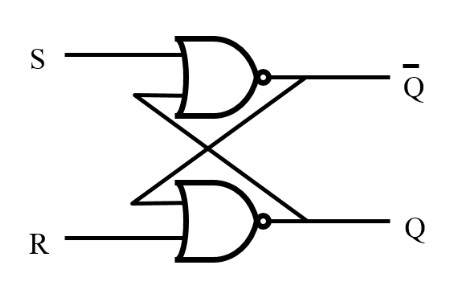

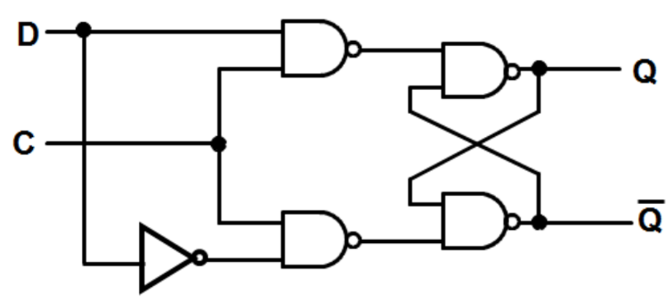

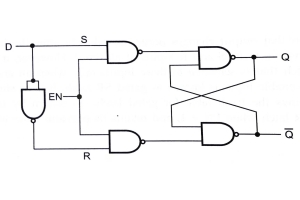

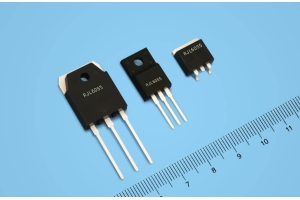

รูปที่ 1: SR latch

SR latch คืออะไร?

สลัก SR หรือ latch ชุด-ชุดเป็นองค์ประกอบการจัดเก็บไบนารีพื้นฐานที่เป็นของหมวดหมู่ของวงจรอะซิงโครนัสซึ่งแตกต่างจากวงจรแบบซิงโครนัส SR latches ทำงานโดยไม่มีสัญญาณนาฬิกาอาศัยการควบคุมสัญญาณอินพุตโดยตรงเท่านั้นสิ่งนี้ช่วยให้พวกเขาทำงานได้อย่างอิสระภายในวงจรดิจิตอลสลัก SR สามารถรักษาสองสถานะที่มั่นคง: สูง (1) และต่ำ (0) ทำให้สามารถเก็บข้อมูลบิตเดียวจนกว่าจะได้รับการอัปเดตโดยสัญญาณอินพุตใหม่

การสร้างสลัก SR โดยทั่วไปจะเกี่ยวข้องกับประตูตรรกะข้ามคู่สองประตูโดยทั่วไปหรือประตูประตูหรือประตู NANDในการออกแบบสลัก SR โดยใช้หรือประตูเอาต์พุตของแต่ละประตูเชื่อมต่อกับอินพุตของอีกฝ่ายการกำหนดค่านี้ช่วยให้มั่นใจได้ว่าสลักสามารถเปลี่ยนสถานะได้อย่างรวดเร็วตามสัญญาณอินพุตในขณะที่รักษาเสถียรภาพจนกว่าอินพุตใหม่จะแจ้งการเปลี่ยนแปลง

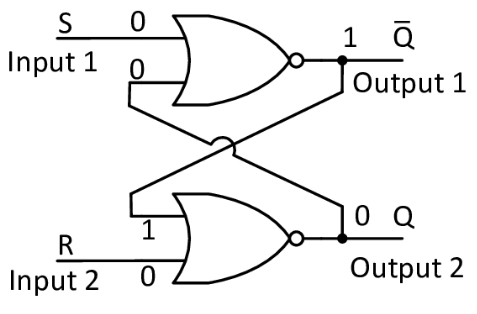

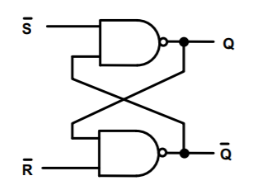

รูปที่ 2: SR latch (2)

ตั้งค่าอินพุต (S): เมื่อเปิดใช้งานชุดอินพุต (S) (สูง), สวิตช์เอาต์พุต latch (q) เป็นสูง (1)

รีเซ็ตอินพุต (R): เมื่อเปิดใช้งานการรีเซ็ต (R) (สูง), สวิตช์เอาต์พุต (q) เป็นต่ำ (0)

อินพุตทั้งสองสูง: หากอินพุตทั้ง S และ R สูงพร้อมกันสลักจะเข้าสู่สถานะที่ไม่ได้กำหนดซึ่งควรหลีกเลี่ยงในการออกแบบ

สลัก SR เป็นสิ่งจำเป็นสำหรับการจัดเก็บข้อมูลชั่วคราวและผลลัพธ์ระดับกลางที่ถืออยู่ในระบบดิจิตอลพวกเขาเป็นองค์ประกอบพื้นฐานในวงจรต่อเนื่องที่ซับซ้อนมากขึ้นเช่นการลงทะเบียนกะหลายบิตหน่วยหน่วยความจำและเคาน์เตอร์บางประเภท

ในแอปพลิเคชันเหล่านี้ SR latches ให้การเก็บข้อมูลที่มั่นคงและสามารถตอบสนองต่อการเปลี่ยนแปลงสัญญาณภายนอกได้อย่างรวดเร็วทำให้มั่นใจได้ว่าการทำงานที่มีประสิทธิภาพของระบบอิเล็กทรอนิกส์ทั้งหมด

แอปพลิเคชั่นที่สำคัญอีกประการหนึ่งของสลัก SR คือการตรวจจับข้อผิดพลาดและตรรกะการแก้ไขภายในวงจรดิจิตอลเนื่องจากความสามารถในการรักษาสถานะที่มั่นคงพวกเขาสามารถตรวจสอบการเปลี่ยนแปลงสถานะของระบบและกลับไปสู่สถานะที่ปลอดภัยที่กำหนดไว้ล่วงหน้าอย่างรวดเร็วเมื่อตรวจจับความผิดปกติคุณลักษณะนี้มีคุณค่าอย่างยิ่งในระบบความน่าเชื่อถือสูงเช่นการบินและอวกาศและอุปกรณ์การแพทย์

สัญลักษณ์ของสลัก SR

การทำความเข้าใจสัญลักษณ์และโครงสร้างของมันเป็นพื้นฐานในการเข้าใจการทำงานและการใช้งานจริงในไดอะแกรมวงจรโดยทั่วไปแล้วสลัก SR จะมีพอร์ตอินพุตหลักสองพอร์ตที่มีป้ายกำกับ S (SET) และ R (รีเซ็ต)อินพุตเหล่านี้ควบคุมสถานะเอาต์พุตของ latch ซึ่งมักจะแสดงเป็น Q. การออกแบบบางอย่างยังมีเอาต์พุตผกผันที่มีป้ายกำกับ Q 'ซึ่งให้สถานะตรงข้ามของ Q

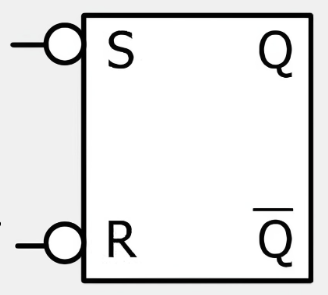

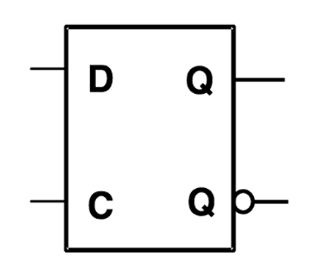

รูปที่ 3: สัญลักษณ์ของสลัก SR

สลัก SR มักจะถูกแทนด้วยสัญลักษณ์สี่เหลี่ยมที่มีอินพุต S และ R และเอาต์พุต Q. ในบางกรณีเอาต์พุต Q 'ก็แสดงขึ้นเช่นกันการติดฉลากที่ชัดเจนนี้ช่วยให้นักออกแบบวงจรสามารถระบุฟังก์ชั่นของส่วนประกอบและบทบาทภายในวงจรขนาดใหญ่ได้อย่างรวดเร็ว

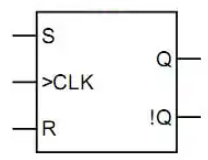

ตัวแปรทั่วไปของสลัก SR รวมถึงอินพุตนาฬิกา (CLK)อินพุต CLK ทำให้มั่นใจได้ว่าการเปลี่ยนแปลงสถานะเกิดขึ้นในการซิงค์กับสัญญาณนาฬิกาทำให้สามารถควบคุมเวลาได้อย่างแม่นยำในการตั้งค่านี้แม้ว่าจะเปิดใช้งาน S หรือ R สถานะของ latch จะอัปเดตเฉพาะเมื่อสัญญาณ CLK ตรงตามเงื่อนไขเฉพาะมักจะอยู่ที่ขอบที่สูงขึ้นหรือลดลงสิ่งนี้จะช่วยป้องกันข้อผิดพลาดที่เกิดจากข้อบกพร่องของสัญญาณอินพุตหรือการเปลี่ยนแปลงที่ไม่ได้ตั้งใจ

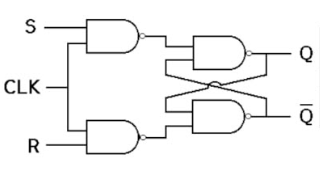

รูปที่ 4: สัญลักษณ์ของสลัก SR ที่มีนาฬิกา

สัญลักษณ์ SR Latch ที่มีการโอเวอร์คล็อกรวมถึงอินพุต S, R และ CLK ภายในสี่เหลี่ยมผืนผ้าการเป็นตัวแทนมาตรฐานนี้ช่วยให้นักออกแบบเข้าใจฟังก์ชั่นของ Latch และข้อกำหนดด้านเวลาตัวอย่างเช่นในการคำนวณประสิทธิภาพสูงหรือระบบการถ่ายโอนข้อมูลที่ซับซ้อนการควบคุม CLK อย่างระมัดระวังทำให้มั่นใจได้ว่าข้อมูลจะถูกจัดเก็บและถ่ายโอนอย่างถูกต้องในแต่ละขั้นตอนการประมวลผลเพื่อเพิ่มประสิทธิภาพของระบบโดยรวมและความน่าเชื่อถือ

การควบคุมอินพุตสลัก SR ที่แม่นยำเป็นสิ่งสำคัญโดยเฉพาะอย่างยิ่งในการออกแบบหน่วยความจำความเร็วสูงและความจุขนาดใหญ่หรือบัฟเฟอร์ข้อมูลชั่วคราวโดยการออกแบบวงจรลอจิกเพื่อจัดการการเปิดใช้งาน S และ R ฟังก์ชั่นที่ซับซ้อนเช่นการโหลดข้อมูลการล้างหรือการรีเซ็ตสถานะสามารถทำได้การควบคุมสัญญาณ CLK ที่แม่นยำช่วยให้มั่นใจได้ว่าการดำเนินการข้อมูลทั้งหมดเป็นไปตามลำดับเวลาที่กำหนดไว้ล่วงหน้าช่วยเพิ่มประสิทธิภาพของระบบและความสามารถในการประมวลผลข้อมูลอย่างมีนัยสำคัญ

ความเข้าใจอย่างลึกซึ้งเกี่ยวกับสัญลักษณ์และโครงสร้างของ SR Latch ไม่เพียง แต่ในการออกแบบวงจรที่ถูกต้องและการแก้ไขปัญหา แต่ยังรวมถึงการดำเนินการตรรกะดิจิตอลที่ซับซ้อนและปรับปรุงประสิทธิภาพของระบบสิ่งนี้มีความสำคัญอย่างยิ่งในการใช้งานที่ต้องการความน่าเชื่อถือและการควบคุมที่แม่นยำเช่นอุปกรณ์การบินและอวกาศและอุปกรณ์การแพทย์

ประเภทของสลักและหลักการทำงานของพวกเขา

สลักเป็นองค์ประกอบพื้นฐานในการออกแบบอิเล็กทรอนิกส์นำเสนอฟังก์ชั่นที่หลากหลายและการใช้งานที่กว้างประเภทหลักของ latches คือสลัก SR และ l latches แต่ละอันมีการดำเนินการที่ไม่ซ้ำกันและกรณีการใช้งาน

SR latch

สลัก SR หรือ latch ชุดรีเซ็ตเป็นอุปกรณ์จัดเก็บข้อมูลพื้นฐานที่ควบคุมโดยอินพุตสองอินพุต S (SET) และ R (รีเซ็ต)

เมื่ออินพุต S ได้รับสัญญาณสูงเอาต์พุต Q จะสูงแสดงว่าข้อมูลจะถูกตั้งค่าเมื่ออินพุต R ได้รับสัญญาณสูงเอาต์พุต Q จะต่ำแสดงว่าข้อมูลจะถูกรีเซ็ตหากอินพุตทั้ง S และ R สูงพร้อมกันสลักจะเข้าสู่สถานะที่ไม่ได้กำหนดทำให้เกิดความไม่แน่นอนของเอาต์พุตที่อาจเกิดขึ้นเงื่อนไขนี้จะต้องหลีกเลี่ยงในการออกแบบการตอบสนองโดยตรงของ SR Latch ต่อสัญญาณอินพุตทำให้มีประโยชน์ในสถานการณ์ที่ต้องการการตอบสนองอย่างรวดเร็ว

d latch

latch D หรือที่เรียกว่า latch data หรือ latch โปร่งใสนำเสนอการควบคุมที่ซับซ้อนมากขึ้นด้วยอินพุตข้อมูล D และสัญญาณนาฬิกา CLK

รูปที่ 5: D latch

รูปที่ 6: d สัญลักษณ์ล็อค

เมื่อ CLK สูงเอาต์พุต Q จะติดตามอินพุต D ทำให้ข้อมูลผ่านสลักได้อย่างอิสระเมื่อ CLK ต่ำกว่าค่าปัจจุบันของ D ถูกล็อคและเอาต์พุต Q จะคงที่จนกว่าสัญญาณ CLK High ถัดไปกลไกนี้ทำให้ D latch เหมาะสำหรับการจัดเก็บข้อมูลชั่วคราวเพื่อซิงโครไนซ์ความเร็วในการประมวลผลที่แตกต่างกันภายในระบบ

SR และ D latches มีบทบาทที่ไม่มีใครเทียบในการจัดเก็บข้อมูลและตรรกะของเครื่องสถานะเนื่องจากการตอบสนองระดับอินพุตโดยตรงสลักจึงมีความสำคัญในการออกแบบวงจรแบบอะซิงโครนัสพวกเขามีฟังก์ชั่นที่สำคัญสำหรับการถ่ายโอนข้อมูลที่ซับซ้อนและระบบการจัดการพลังงานจัดเก็บข้อมูลสถานะอย่างมีประสิทธิภาพเพื่อให้แน่ใจว่าการทำงานที่มั่นคงการใช้สลักที่เหมาะสมเหล่านี้สามารถปรับปรุงความน่าเชื่อถือและประสิทธิภาพของวงจรได้อย่างมีนัยสำคัญทำให้พวกเขาขาดไม่ได้ในระบบอิเล็กทรอนิกส์ที่ทันสมัย

ตารางความจริงของสลัก SR

รูปที่ 7: sr nand latch

|

S |

R |

ถาม |

ถาม ' |

บันทึก |

|

0 |

0 |

1 |

1 |

ต้องห้าม |

|

0 |

1 |

1 |

0 |

ชุด |

|

1 |

0 |

0 |

1 |

รีเซ็ต |

|

1 |

1 |

ถาม |

ถาม ' |

รักษาไว้ |

แผนภูมิ 1: ตารางความจริงของ SR latch โดยใช้ Nand Gates

รูปที่ 8: SR หรือ latch

|

S |

R |

ถาม |

ถาม ' |

บันทึก |

|

0 |

0 |

ถาม |

ถาม ' |

รักษาไว้ |

|

0 |

1 |

1 |

0 |

รีเซ็ต |

|

1 |

0 |

0 |

1 |

ชุด |

|

1 |

1 |

0 |

0 |

ต้องห้าม |

แผนภูมิ 2: ตารางความจริงของ SR latch โดยใช้หรือประตู

ตอนนี้เราใช้ตารางความจริงของสลัก SR โดยใช้ NOR GATE เป็นตัวอย่างเพื่อทำความเข้าใจความหมายของตารางความจริงของสลัก SR

สถานะอินพุตและเอาต์พุต

ทั้ง S และ R คือ 0: สลักยังคงอยู่ในสถานะปัจจุบันเอาต์พุต Q ยังคงเหมือนเดิมไม่ว่าจะเป็น 0 หรือ 1

S คือ 0 และ R คือ 1: สลักรีเซ็ตบังคับให้เอาต์พุต Q ถึง 0

S คือ 1 และ R คือ 0: ชุดสลักทำให้เอาต์พุต Q เท่ากับ 1

ทั้ง S และ R คือ 1: เงื่อนไขนี้ไม่ถูกต้องหรือไม่ได้กำหนดมักจะเรียกว่าสถานะ "ต้องห้าม" ในสลัก SRในกรณีนี้ Q และ Q 'ทั้งคู่เท่ากับ 0 นำไปสู่ผลลัพธ์ที่คลุมเครือ

เมื่อ S และ R เป็นทั้ง 0 สลักจะไม่ทำอะไรเลยและเก็บค่าปัจจุบันไว้สิ่งนี้มีประโยชน์สำหรับการรักษาสถานะโดยไม่มีการเปลี่ยนแปลง

เมื่อ S คือ 0 และ R คือ 1 สลักจะถูกบอกให้รีเซ็ตอย่างชัดเจนตรวจสอบให้แน่ใจว่า Q คือ 0 โดยไม่คำนึงถึงสถานะก่อนหน้านี้นี่เป็นวิธีที่ตรงไปตรงมาในการล้างสลัก

เมื่อ S คือ 1 และ R คือ 0 สลักจะถูกตั้งค่าให้แน่ใจว่า Q กลายเป็น 1 นี่คือวิธีที่คุณเก็บ '1' ไว้ในสลัก

เมื่อ S และ R เป็นทั้ง 1 สถานะไม่ได้รับอนุญาตเพราะมันทำให้ทั้งสองเอาต์พุตเป็น 0 ซึ่งขัดแย้งและไม่น่าเชื่อถือนักออกแบบจะต้องหลีกเลี่ยงเงื่อนไขนี้เพื่อให้แน่ใจว่าการทำงานที่มั่นคง

ข้อดีและข้อเสียของสลัก

สลักมีการใช้กันอย่างแพร่หลายในการออกแบบวงจรดิจิตอลเนื่องจากความเรียบง่ายและต้นทุนต่ำลักษณะเหล่านี้ช่วยให้ลัตช์ทำงานด้วยความเร็วสูงด้วยการใช้พลังงานต่ำทำให้เหมาะสำหรับระบบดิจิตอลความเร็วสูงตัวอย่างเช่นในไฟล์การลงทะเบียนโปรเซสเซอร์ latches สามารถจัดเก็บและดึงข้อมูลได้อย่างรวดเร็วเพิ่มความเร็วและประสิทธิภาพการประมวลผลอย่างมีนัยสำคัญ

ข้อดีของสลัก

ความเรียบง่ายและความคุ้มค่า: สลักเป็นส่วนประกอบที่ตรงไปตรงมาซึ่งราคาไม่แพงในการใช้งานในวงจรดิจิตอล

ความเร็วสูงและพลังงานต่ำ: การออกแบบของพวกเขาช่วยให้สามารถใช้งานได้อย่างรวดเร็วด้วยการใช้พลังงานน้อยที่สุดซึ่งมีความสำคัญในระบบดิจิตอลความเร็วสูง

ประสิทธิภาพในการจัดการข้อมูล: ในแอปพลิเคชันเช่นไฟล์การลงทะเบียนโปรเซสเซอร์ latches ให้การจัดเก็บข้อมูลอย่างรวดเร็วและการดึงข้อมูลเพิ่มประสิทธิภาพของระบบโดยรวม

ข้อเสียของสลัก

แม้จะมีข้อดีของพวกเขา latches มีข้อ จำกัด ที่โดดเด่นในการออกแบบและแอปพลิเคชันบางอย่าง

พฤติกรรมที่คาดเดาไม่ได้ในการออกแบบแบบอะซิงโครนัส: หากไม่มีการควบคุมสัญญาณนาฬิกา latches สามารถทำตัวไม่แน่นอนใน SR latches ถ้าทั้งชุด (S) และรีเซ็ต (R) อินพุตสูงพร้อมกันเอาต์พุตจะไม่ได้กำหนดซึ่งนำไปสู่ความไม่แน่นอนนี่เป็นปัญหาในการควบคุมแบบเรียลไทม์หรือแอพพลิเคชั่นที่สำคัญต่อความปลอดภัยซึ่งผลลัพธ์ที่เชื่อถือได้นั้นเป็นสิ่งสำคัญ

การออกแบบเวลาที่ซับซ้อน: การออกแบบด้วยสลักต้องมีการพิจารณาเวลาอย่างระมัดระวังวิศวกรจะต้องอธิบายถึงความล่าช้าในการแพร่กระจายสัญญาณและเงื่อนไขการแข่งขันเพื่อหลีกเลี่ยงข้อผิดพลาดในการกำหนดเวลาการออกแบบที่ไม่เหมาะสมอาจส่งผลให้เกิดการเปลี่ยนแปลงข้อมูลก่อนที่สัญญาณนาฬิกาจะเสถียรทำให้เกิดความเสียหายของข้อมูลหรือการจับข้อมูลที่ไม่ถูกต้องสิ่งนี้จำเป็นต้องมีความเข้าใจอย่างลึกซึ้งเกี่ยวกับการวิเคราะห์เวลาและพฤติกรรมวงจร

เพื่อจัดการกับความท้าทายเหล่านี้สามารถใช้เทคนิคและกลยุทธ์การออกแบบที่เฉพาะเจาะจงได้:

กลไกการซิงโครไนซ์: การเพิ่มกลไกการซิงโครไนซ์สามารถช่วยจัดการอินพุตแบบอะซิงโครนัสและลดพฤติกรรมที่คาดเดาไม่ได้

การจัดการนาฬิกาที่กำหนดเอง: การใช้กลยุทธ์การจัดการนาฬิกาที่กำหนดเองสามารถมั่นใจได้ว่าข้อมูลนั้นถูกล็อคอย่างถูกต้องและในเวลาที่เหมาะสม

การใช้เครื่องมือ EDA: เครื่องมือการออกแบบอัตโนมัติแบบอิเล็กทรอนิกส์ (EDA) ที่ทันสมัยนำเสนอการวิเคราะห์ขั้นสูงและความสามารถในการเพิ่มประสิทธิภาพเครื่องมือเหล่านี้ช่วยทำนายและแก้ไขปัญหาเวลาและการซิงโครไนซ์ในระหว่างขั้นตอนการออกแบบปรับปรุงความน่าเชื่อถือและประสิทธิภาพของระบบดิจิตอลโดยใช้ latchesพวกเขาช่วยนักออกแบบในการระบุปัญหาที่อาจเกิดขึ้นในช่วงต้นเพื่อให้มั่นใจว่าผลิตภัณฑ์ขั้นสุดท้ายทำงานได้อย่างน่าเชื่อถือภายใต้เงื่อนไขต่าง ๆ

การใช้งานจริงของสลัก SR

SR latches เป็นที่รู้จักกันดีในความสามารถในการรักษาสถานะอย่างรวดเร็วและน่าเชื่อถือมีการใช้กันอย่างแพร่หลายในระบบอิเล็กทรอนิกส์ต่างๆพวกเขาเก่งในสถานการณ์ที่ต้องการการจัดเก็บข้อมูลชั่วคราวหรือการเก็บรักษาสถานะ

การจัดเก็บข้อมูลชั่วคราว

สลัก SR มักใช้ในหน่วยความจำแคชเพื่อจัดเก็บข้อมูลชั่วคราวสิ่งนี้ช่วยให้ระบบสามารถเข้าถึงข้อมูลที่ใช้บ่อยได้อย่างรวดเร็วเพิ่มความสามารถในการประมวลผลข้อมูลและประสิทธิภาพของโปรเซสเซอร์ขนาดใหญ่

ไฟล์การลงทะเบียนที่เก็บข้อมูล

ในโปรเซสเซอร์ SR latches เปิดใช้งานการจัดเก็บอย่างรวดเร็วและการดึงข้อมูลในไฟล์ลงทะเบียนเพิ่มความเร็วในการประมวลผลและประสิทธิภาพของระบบโดยรวม

การรักษาสัญญาณควบคุม

ในระบบควบคุมดิจิตอลสลัก SR มีประโยชน์ในการรักษาสถานะของสัญญาณควบคุมบางอย่างจนกว่าจะมีเงื่อนไขภายนอกหรือตรรกะของระบบกำหนดการเปลี่ยนแปลงนอกจากนี้พวกเขายังช่วยในการรักษาสถานะภายในระบบเพื่อให้มั่นใจถึงประสิทธิภาพที่สอดคล้องกันในการดำเนินงานที่ต้องการความแม่นยำและความน่าเชื่อถือ

ทริกเกอร์และเคาน์เตอร์วงจร

รองเท้าแตะที่ใช้ SR latch มักใช้ในวงจรที่ต้องใช้การทำงานแบบซิงโครไนซ์เช่นนาฬิกาดิจิตอลและตัวจับเวลาพวกเขาควบคุมจำนวนพัลส์เพื่อให้มั่นใจว่าการจับเวลาเวลาที่แม่นยำและประสิทธิภาพที่เชื่อถือได้วงจรเหล่านี้พึ่งพาสลัก SR เพื่อรักษาจำนวนที่แม่นยำซึ่งอำนวยความสะดวกในการกำหนดเวลาและการจัดลำดับในระบบดิจิตอล

การโต้ตอบเชิงกล

สลัก SR มีประสิทธิภาพในการกำจัดการตีกลับเชิงกลในสวิตช์การตีกลับเชิงกลเกิดขึ้นเมื่อสวิตช์สร้างการเปลี่ยนแปลงสัญญาณซ้ำ ๆ ซ้ำ ๆ เนื่องจากการสัมผัสที่ไม่ดีSR latches ทำให้สัญญาณเอาต์พุตเสถียรป้องกันข้อผิดพลาดที่เกิดจากสัญญาณที่มีเสียงดัง

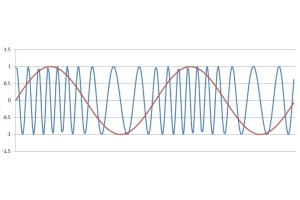

SR Flip-Flop

SR Flip-Flop ซึ่งมักเรียกว่า Flip-Flop ชุดที่ถูกเรียกใช้ขอบซึ่งประกอบด้วยสลัก SR ที่เชื่อมต่อกันสองตัวโครงสร้างคู่ลัตช์นี้ช่วยให้สามารถตอบสนองต่อขอบสัญญาณนาฬิกาที่เฉพาะเจาะจง (เพิ่มขึ้นหรือลดลง) เพื่อเปลี่ยนสถานะนี่คือความสำเร็จผ่านการควบคุมตรรกะพิเศษระหว่างสลักเอาต์พุตของสลักแรกกลายเป็นส่วนหนึ่งของอินพุตสำหรับสลักที่สองและเอาต์พุตของสลักที่สองในทางกลับกันมีอิทธิพลต่อสลักแรกสร้างลูปตอบกลับแบบประสาน

รูปที่ 7: SR Flip-Flop

SR Flip-Flop เปลี่ยนสถานะอย่างแม่นยำที่ขอบของสัญญาณนาฬิกาที่เพิ่มขึ้นหรือลดลงข้อเสนอแนะที่เชื่อมต่อกันระหว่างล็อค SR ทั้งสองช่วยให้มั่นใจได้ว่า Flip-Flop จะเปลี่ยนสถานะเฉพาะในการตอบสนองต่อขอบนาฬิกาให้เอาต์พุตที่เสถียรและเชื่อถือได้

ในไมโครโปรเซสเซอร์และโปรเซสเซอร์สัญญาณดิจิตอล SR Flip-Flop ใช้สำหรับการสุ่มตัวอย่างข้อมูลและการจัดเก็บข้อมูลพวกเขาจับภาพและทำให้ข้อมูลมีเสถียรภาพที่ขอบนาฬิกาที่ระบุเพื่อให้มั่นใจว่าการประมวลผลและการวิเคราะห์ข้อมูลที่เชื่อถือได้ในภายหลัง

กลไกการกระตุ้นขอบช่วยหลีกเลี่ยงสภาพการแข่งขันซึ่งส่วนต่าง ๆ ของวงจรอาจเปลี่ยนสถานะในเวลาเดียวกันโดยไม่ต้องซิงโครไนซ์ซึ่งอาจส่งผลให้เกิดเอาต์พุตที่ไม่เสถียรหรือไม่ถูกต้องSR Flip-Flops มีความสำคัญในการใช้ตรรกะการสื่อสารที่เฉพาะเจาะจงเช่นการซิงโครไนซ์เฟรมและการตรวจจับข้อผิดพลาดความเสถียรและเวลาตอบสนองที่รวดเร็วของพวกเขาช่วยรักษาคุณภาพการส่งข้อมูลและความน่าเชื่อถือของระบบ

รัฐต้องห้ามใน SR latches และ SR Flip-Flops

เมื่อออกแบบสลัก SR และรองเท้าแตะ SR โดยใช้ NAND และ NOR GATES เราทุกคนต้องให้ความสนใจกับการจัดการและหลีกเลี่ยงสถานะที่ถูกยับยั้งสถานะต้องห้ามเกิดขึ้นเมื่อทั้งชุดอินพุต (S) และรีเซ็ต (R) สูงพร้อมกัน (สำหรับประตู NAND) หรือต่ำ (สำหรับประตู NOR)การรวมกันนี้นำไปสู่สถานะเอาต์พุตที่ไม่แน่นอนเนื่องจากเอาต์พุตขึ้นอยู่กับสถานะก่อนหน้าของวงจรทำให้ไม่สามารถคาดเดาได้

รัฐต้องห้ามใน NAND Gate SR latches

เมื่อทั้ง S และ R ต่ำทั้งสองเอาต์พุตจะสูงซึ่งละเมิดลักษณะเอาต์พุตเสริมของ latchสิ่งนี้ส่งผลให้สถานะไม่แน่นอน

รัฐต้องห้ามในและประตู SR latches

เมื่อทั้ง S และ R สูงทั้งสองเอาต์พุตจะต่ำและสร้างสถานะที่ไม่แน่นอนสิ่งนี้สามารถนำไปสู่พฤติกรรมที่คาดเดาไม่ได้ในวงจร

แนวทางปฏิบัติเพื่อหลีกเลี่ยงรัฐต้องห้าม

การเพิ่มตรรกะการควบคุม

ใช้ประตูตรรกะเพิ่มเติมเพื่อตรวจสอบสถานะของ S และ R หากอินพุตทั้งสองมีแนวโน้มไปสู่สถานะต้องห้ามให้ปรับอินพุตหนึ่งอินพุตโดยอัตโนมัติเพื่อป้องกันสถานะที่ไม่แน่นอนสิ่งนี้ทำให้มั่นใจได้ว่าเอาต์พุตยังคงมีเสถียรภาพและคาดการณ์ได้ใช้ประตูตรรกะที่แทรกแซงเมื่อ S และ R มีทั้งสูง (หรือต่ำ) ปรับอินพุตหนึ่งอินพุตเพื่อรักษาสถานะที่ถูกต้อง

การจำลองซอฟต์แวร์และการทดสอบฮาร์ดแวร์

ดำเนินการจำลองซอฟต์แวร์อย่างละเอียดเพื่อระบุสถานะต้องห้ามที่อาจเกิดขึ้นภายใต้เงื่อนไขการดำเนินงานต่างๆสิ่งนี้ช่วยให้นักออกแบบสามารถมองเห็นและแก้ไขข้อผิดพลาดเชิงตรรกะก่อนการใช้งานทางกายภาพทำการทดสอบฮาร์ดแวร์อย่างกว้างขวางเพื่อตรวจสอบว่าวงจรจัดการชุดค่าผสมทั้งหมดอย่างถูกต้องขั้นตอนนี้ช่วยให้แน่ใจว่าสลักหรือฟลิปฟล็อปทำงานได้อย่างน่าเชื่อถือในสถานการณ์จริง

บทสรุป

ความเก่งกาจและความน่าเชื่อถือของ SR latches เน้นย้ำความสำคัญของพวกเขาในการออกแบบวงจรดิจิตอลด้วยการสำรวจพฤติกรรมที่เหมาะสมที่สุดของ SR latches ผ่านการเป็นตัวแทนสัญลักษณ์ตารางความจริงและการใช้งานจริงเราได้รับความเข้าใจที่ครอบคลุมเกี่ยวกับการดำเนินงานและความสำคัญของพวกเขาแม้จะมีข้อผิดพลาดที่อาจเกิดขึ้นของรัฐที่ไม่ได้กำหนดในการออกแบบแบบอะซิงโครนัส แต่การดำเนินการเชิงกลยุทธ์ของตรรกะการควบคุมและการจำลองที่กว้างขวางสามารถลดความเสี่ยงเหล่านี้ได้เครื่องมือการออกแบบระบบอัตโนมัติทางอิเล็กทรอนิกส์ขั้นสูง (EDA) ช่วยเพิ่มความน่าเชื่อถือและประสิทธิภาพของวงจรที่รวมเอาสลัก SR โดยการทำนายและแก้ไขปัญหาเวลาและการซิงโครไนซ์ไม่ว่าจะใช้ในการจัดเก็บข้อมูลชั่วคราวการบำรุงรักษาสัญญาณควบคุมหรือการตรวจจับข้อผิดพลาด SR latches พิสูจน์ให้เห็นว่าเป็นพื้นฐานในการสร้างระบบดิจิตอลที่แข็งแกร่งและมีประสิทธิภาพบทบาทของพวกเขาในการดำเนินการหน่วยความจำความเร็วสูงและการประมวลผลข้อมูลแบบซิงโครนัสในแอปพลิเคชันที่ซับซ้อนเป็นตัวอย่างของความเกี่ยวข้องที่ยั่งยืนในขณะที่เทคโนโลยีก้าวหน้าหลักการที่ควบคุมการล็อค SR ยังคงแจ้งและสร้างแรงบันดาลใจนวัตกรรมในอุปกรณ์อิเล็กทรอนิกส์ดิจิตอลเพื่อให้มั่นใจว่าส่วนประกอบระดับประถมเหล่านี้ยังคงเป็นส่วนสำคัญในการพัฒนาอุปกรณ์อิเล็กทรอนิกส์ที่ซับซ้อนและเชื่อถือได้

คำถามที่พบบ่อย [คำถามที่พบบ่อย]

1. สลัก SR คืออะไร?

สลัก SR หรือ latch ชุดรีเซ็ตเป็นองค์ประกอบการจัดเก็บไบนารีพื้นฐานที่ใช้ในวงจรดิจิตอลมันเป็นวงจรแบบอะซิงโครนัสซึ่งหมายความว่าทำงานโดยไม่มีสัญญาณนาฬิกาอาศัยการควบคุมโดยตรงของอินพุตเพื่อเปลี่ยนสถานะ

2. ฟังก์ชั่นของ SR ในตรรกะคืออะไร?

ในตรรกะอินพุต SR (Set-Reset) ควบคุมสถานะของสลัก

3. SR Latch ใช้เกตประเภทใด

โดยทั่วไปแล้วสลัก SR จะใช้ประตู NOR หรือประตู NANDในสลัก SR ที่ใช้เกทตามเกตเอาท์พุทของแต่ละประตูและเกตจะถูกป้อนกลับเข้าไปในอินพุตของอีกฝ่ายในสลัก SR ที่ใช้เกต NAND จะใช้การกำหนดค่าความคิดเห็นที่คล้ายกัน แต่ระดับตรรกะจะกลับด้านเมื่อเทียบกับสลักที่ใช้เกต NORการกำหนดค่าทั้งสองบรรลุฟังก์ชั่นพื้นฐานเดียวกันของการรักษาสถานะไบนารีตามชุดและรีเซ็ตอินพุต

4. สลักทำงานอย่างไร?

สลักทำงานโดยใช้ข้อเสนอแนะเพื่อรักษาสถานะเอาต์พุตตามอินพุตที่ให้ไว้ในสลัก SR ชุดอินพุต (S) และรีเซ็ต (R) ควบคุมสถานะของเอาต์พุต (q)เมื่อเปิดใช้งานชุดอินพุต (สูง) เอาต์พุตจะถูกตั้งค่าเป็นสูง (1)เมื่อเปิดใช้งานอินพุตรีเซ็ต (สูง) เอาต์พุตจะถูกรีเซ็ตเป็นต่ำ (0)ลูปข้อเสนอแนะในการออกแบบของ latch ทำให้มั่นใจได้ว่าเมื่อสถานะเอาต์พุตถูกสร้างขึ้นมันจะยังคงมีเสถียรภาพจนกว่าสัญญาณอินพุตใหม่จะเปลี่ยนไป

5. ข้อเสียของสลัก SR คืออะไร?

ข้อเสียปฐมภูมิของสลัก SR คือสถานะที่ไม่ได้กำหนดซึ่งเกิดขึ้นเมื่อทั้งชุดอินพุตและรีเซ็ต (R) สูงพร้อมกันเงื่อนไขนี้นำไปสู่สถานะเอาต์พุตที่ไม่แน่นอนซึ่งอาจทำให้เกิดความไม่แน่นอนและพฤติกรรมที่คาดเดาไม่ได้ในวงจรดิจิตอลสถานะ "ต้องห้าม" นี้จะต้องหลีกเลี่ยงการออกแบบเพื่อให้แน่ใจว่าการทำงานที่เชื่อถือได้

SR latch, latch ชุด-ชุด, วงจรแบบอะซิงโครนัส, องค์ประกอบการจัดเก็บไบนารี, วงจรดิจิตอล, หรือประตู, ประตู NAND, ลูปตอบรับ, สถานะสูง, สถานะต่ำ, สถานะที่ไม่ได้กำหนด, สัญญาณนาฬิกา, การควบคุมโดยตรง, การจัดเก็บข้อมูลชั่วคราวการตรวจจับข้อผิดพลาด, แอปพลิเคชันการบินและอวกาศ, อุปกรณ์การแพทย์, การออกแบบวงจร, สลัก SR โอเวอร์คล็อต, สัญญาณอินพุต, สัญลักษณ์และโครงสร้าง, หน่วยความจำความเร็วสูง, บัฟเฟอร์ข้อมูล, การควบคุมเวลา, การควบคุมที่แม่นยำ, การเก็บรักษาสถานะ, ไมโครโปรเซสเซอร์, โปรเซสเซอร์สัญญาณดิจิตอล, การสุ่มตัวอย่างข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูล, ข้อมูลการจัดเก็บ, การกระตุ้นขอบ, SR Flip-Flop, ข้อเสนอแนะที่เชื่อมต่อกัน, เงื่อนไขการแข่งขัน, ตรรกะโปรโตคอลการสื่อสาร, การซิงโครไนซ์เฟรม, การตรวจจับข้อผิดพลาด, ข้อบกพร่องสัญญาณ, การออกแบบอิเล็กทรอนิกส์อัตโนมัติ, เครื่องมือ EDA, กลไกการซิงโครไนซ์, การจัดการนาฬิกาที่กำหนดเอง, ข้อผิดพลาดเวลา, ความล่าช้าในการเผยแพร่เงื่อนไขการแข่งขัน, การถ่ายโอนข้อมูลที่ซับซ้อน, ระบบการจัดการพลังงาน, การตีกลับเชิงกล, การใช้งานจริง, ระบบควบคุมดิจิตอล, ประตูตรรกะ, การจำลองซอฟต์แวร์, การทดสอบฮาร์ดแวร์, สถานะต้องห้าม, ความน่าเชื่อถือของล็อค

เกี่ยวกับเรา

ALLELCO LIMITED

อ่านเพิ่มเติม

สอบถามรายละเอียดเพิ่มเติมอย่างรวดเร็ว

กรุณาส่งคำถามเราจะตอบกลับทันที

คำแนะนำเกี่ยวกับพื้นฐานของ D Flip -Flop - วงจร, ตารางความจริง, ประเภท, ข้อดีและข้อ จำกัด

บน 17/05/2024

คู่มือเปรียบเทียบการวิเคราะห์ rheostat และ potentiometers

บน 17/05/2024

โพสต์ยอดนิยม

-

GND ในวงจรคืออะไร?

บน 01/01/1970 3274

-

คู่มือเชื่อมต่อ RJ-45: รหัสสีตัวเชื่อมต่อ RJ-45, แผนการเดินสาย, แอปพลิเคชัน R-J45, RJ-45 Datasheets

บน 01/01/1970 2817

-

การทำความเข้าใจแรงดันไฟฟ้าของแหล่งจ่ายไฟในอิเล็กทรอนิกส์ VCC, VDD, VEE, VSS และ GND

บน 20/11/0400 2645

-

ประเภทตัวเชื่อมต่อไฟเบอร์: SC vs LC และ LC กับ MTP

บน 01/01/1970 2266

-

การเปรียบเทียบระหว่าง DB9 และ RS232

บน 01/01/1970 1883

-

แบตเตอรี่ LR44 คืออะไร?

กระแสไฟฟ้าที่ใช้กำลังแพร่หลายแทรกซึมทุกแง่มุมของชีวิตประจำวันของเราตั้งแต่อุปกรณ์เล็กน้อยไปจนถึงอุปกรณ์การแพทย์ที่คุกคามชีวิตมันมีบทบาทเงียบอย่างไรก็ตามการเข้าใจพลังงานนี้อย่างแท้จริงโดยเฉพาะอย่างยิ่ง...บน 01/01/1970 1846

-

การทำความเข้าใจพื้นฐาน: การต่อต้านการเหนี่ยวนำและความสามารถพิเศษ

ในการเต้นรำที่ซับซ้อนของวิศวกรรมไฟฟ้าทั้งสามองค์ประกอบพื้นฐานต้องใช้เวทีกลาง: การเหนี่ยวนำความต้านทานและความจุแต่ละหมีมีลักษณะเฉพาะที่กำหนดจังหวะแบบไดนามิกของวงจรอิเล็กทรอนิกส์ที่นี่เราเริ่มต้นการเดินท...บน 01/01/1970 1809

-

คู่มือการใช้แบตเตอรี่ CR2430: ข้อมูลจำเพาะแอปพลิเคชันและการเปรียบเทียบกับแบตเตอรี่ CR2032

แบตเตอรี่ CR2430 คืออะไร?ประโยชน์ของแบตเตอรี่ CR2430บรรทัดฐานแอปพลิเคชันแบตเตอรี่ CR2430CR2430 เทียบเท่าCR2430 เทียบกับ CR2032ขนาดแบตเตอรี่ CR2430สิ่งที่จะมองหาเมื่อซื้อ CR2430 และเทียบเท่าแผ่นข้อมูล PDFคำถามที่พบบ่อย แบตเตอรี่เป็นห...บน 01/01/1970 1802

-

RF คืออะไรและทำไมเราถึงใช้มัน?

เทคโนโลยีความถี่วิทยุ (RF) เป็นส่วนสำคัญของการสื่อสารไร้สายที่ทันสมัยทำให้สามารถส่งข้อมูลในระยะทางไกลได้โดยไม่ต้องเชื่อมต่อทางกายภาพบทความนี้นำเสนอพื้นฐานของ RF อธิบายว่ารังสีแม่เหล็กไฟฟ้า (EMR) ทำให้การสื่อส...บน 01/01/1970 1801

-

คู่มือที่ครอบคลุมถึง HFE ในทรานซิสเตอร์

ทรานซิสเตอร์เป็นส่วนประกอบสำคัญในอุปกรณ์อิเล็กทรอนิกส์ที่ทันสมัยช่วยให้การขยายสัญญาณและการควบคุมบทความนี้นำเสนอความรู้เกี่ยวกับ HFE รวมถึงวิธีการเลือกค่า HFE ของทรานซิสเตอร์วิธีการค้นหา HFE และการได้รับทรานซ...บน 20/11/5600 1782